2. 都柏林大学 电气与电子工程学院, D04 V1W8 爱尔兰 都柏林

2. School of Electrical and Electronic Engineering, University College Dublin, D04 V1W8 Dublin, Ireland

随着CMOS工艺进入深亚微米时代,大型数字逻辑模块间的互连线连接变得日益复杂.超长互连线不可避免地出现在片上系统及多核处理器等复杂的数字系统中[1-4].但是,超长互连线引入的大量寄生参数严重阻碍了数字系统的速度和功耗.所以,如何解决信号在长互连线上快速且低功耗的传递成为设计高速数字集成电路的关键.传统在互连线上等间距插入缓冲器的做法,在高速电路中将增加大量功耗,已经不再适用.电流模互连电路作为解决互连线上信号传递问题最有潜力的解决方案之一已经被广泛研究.文献[1-2]中提出了电容耦合驱动器的电流模式电路.在90 nm工艺,驱动10 mm长互连线的测试中,该方法与插入缓冲器的方法相比获得了85%的功耗性能提升.文献[3-9]则提出了动态电流源结构(dynamic overdriving),这种结构具有两套开关电流源:强驱动电流源和弱驱动电流源,较好地兼顾了速度和功耗性能的矛盾.

电流模互连电路的设计属于模拟电路设计范畴,但是由于短沟道效应,如:纵向电场导致的迁移率退化,水平电场导致的速度饱和效应,平方律对于深亚微米的CMOS电路中MOSFETs的尺寸确定已经不再适用. 1996年,F. Silveira等[10]提出了一种新的电路设计方法—基于gm/ID的设计方法学.这种方法提出了一种新的特征参数,即电流效率gm/ID,用以表征单位电流强度的跨导.通过仿真单个管子基于此参数(gm/ID)的单位宽度的电流强度(ID/W),制成设计表格,通过查表的方式来得到管子的宽W.这种设计方式的准确性较高,因为各种短沟道效应已经通过仿真被包含进了设计表格中. D. Foty在F. Silveira的研究基础上,用gm/ID的方法重新阐述了深亚微米时代MOS管的种种短沟道效应[11]. B. E. Boser[12]提出用设计参数2ID/gm,代替gm/ID,使得该方法和传统的基于过驱动电压的设计能够很好结合,因为在长沟道条件下的饱和区管子2ID/gm就是过驱动电压. P. Jespers系统的总结了gm/ID的设计理论,认为这是在深亚微米工艺下一种确定管子尺寸的优良工具[13]. Stanford的Boris Murmann等[14]提出了用5种特征参数gm/ID,gm/gds,gm/cgs,cgd/cgs, cdb/cgs,来描述一个管子,其中cgd/cgs和cdb/cgs可以用来预测管子的寄生电容特性.

本文提出一种模拟电路快速设计方法并应用于文献[15]提出的电流模式互连电路的设计中,其首先基于MATLAB对电流模电路建模找到优化的功耗设计指标,然后运用2ID/gm方法快速确定电流模电路中MOS管的尺寸.这一套方法,亦可应用在其他深亚微米模拟集成电路的设计中.接下本文介绍了应用于电流模电路的2ID/gm方法的设计流程;并将该方法应用到电流模电路的设计中,证明此方法的有效性.

1 2ID/gm的设计流程本节系统介绍应用在电流模式互连电路设计中的2ID/gm方法.由于电流模式互连电路设计不需要估算Cgd和Cdb,对MOS管的本征增益也没有要求,故本文不对电容系数Cgd/Cgs,Cdb/Cgs以及MOS管本征增益gmgds说明,只研讨和电流模电路设计相关的“类过驱动电压”2ID/gm和速度效率指标fT *gm/ID.由此,归纳出应用在电流模式互连电路设计中的2ID/gm方法.

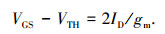

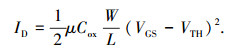

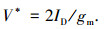

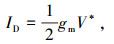

1.1 短沟道MOS管的类过驱动电压V*长沟道模拟集成电路设计中,常常关心一个MOS管的3个指标:跨导gm,源极电流ID,以及过驱动电压VGS-VTH.对于饱和区的MOS管他们之间的关系可写为

|

(1) |

根据电路频率响应,功耗等指标,确定出上述3个指标的任意两个,便可依据MOS管平方律推算出MOS管的宽长比,即

|

(2) |

但是在深亚微米工艺中,由于MOS管内横向电场导致的速度饱和效应和纵向电场导致的迁移率退化效应,迁移率μ的大小是不固定的,它与沟道长度L和过驱动电压VGS-VTH都有关.所以,深亚微米工艺下,MOS管的平方律已经失效了.但是,可以沿用式(1)的定义,得到一个新的物理量:类过驱动电压,计算公式为

|

(3) |

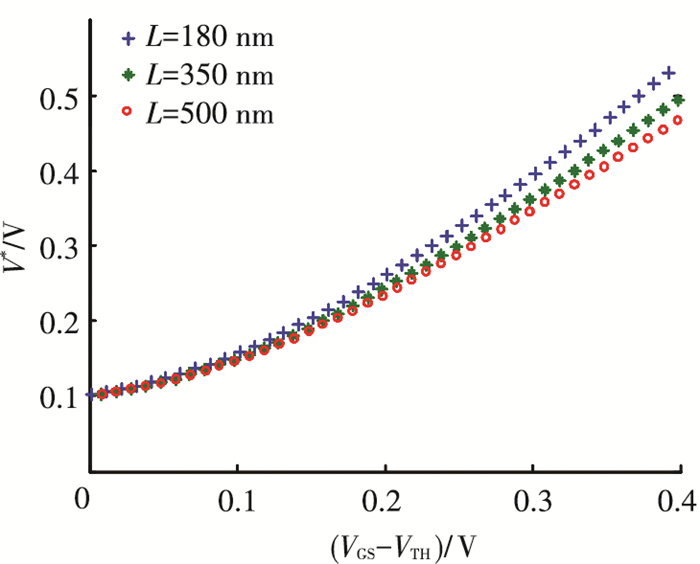

用以表征MOS管产生每单位跨导所需的直流的大小.原来在设计MOS管时,挑选过驱动电压的大小,现在变为挑选类过驱动电压的大小.过驱动电压VGS-VTH和类过驱动电压V*,正相关但并不相等,如图 1、2所示.对式(3)变形,得

|

(4) |

|

图 1 电流效率gm/ ID仿真电路 |

|

图 2 过驱动电压与类过驱动电压V*的关系 |

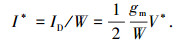

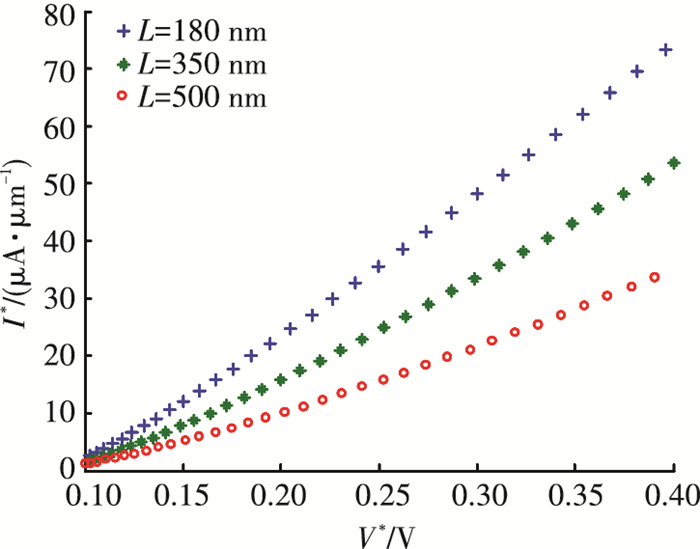

两边同时除以W得到,某一V*和L下每单位宽度电流为

|

(5) |

其中gm/W与MOS管的长度L和过驱动电压VGS-VTH(或类过驱动电压V*)相关,与MOS管宽度无关.即选定MOS管L和类过驱动电压后,有唯一的每单位宽度电流I*与之对应.

将NMOS接成二极管接法,如图 1所示,扫VGS电压,在不同直流工作点下,让SPICE分别计算2ID/gm(V*)和ID/W(I*),得到图 2类过驱动电压V*与过驱动电压的关系,以及图 3每单位宽度电流I*与类过驱动电压V*的关系.由图 2可以观察到类过驱动电压正相关于过驱动电压.

|

图 3 类过驱动电压V*与每单位宽度电流I*的关系 |

假设根据频率响应的需求计算出MOS管所需的gm,再挑选相应的V*,由式(4)计算得到ID.接着,通过查找图 3得到该V*对应的I*,根据W=ID/I*,即可得到MOS管的宽度W.或者,直接由功耗或者别的约束条件确定ID,挑选V*,查找图 3得到对应的I*,根据W=ID/I*即可得到MOS管的宽度W.由于图 3中的曲线,是由SPICE模型仿真得到,已包含了各种短沟道效应,所以这种模拟电路设计方法,能非常准确得到MOS管设计尺寸的初值.

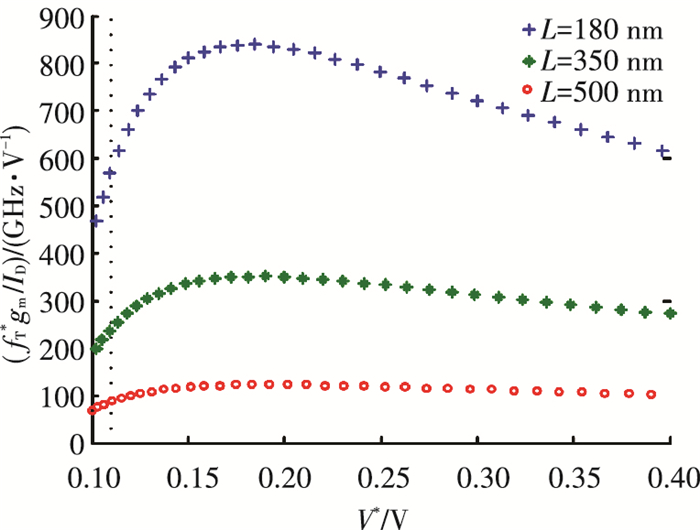

1.2 速度效率指标fT* gm/ID在1.1节中,引入了基于类过驱动电压确定MOS管参数的方法.由于类过驱动电压正相关于过驱动电压(见图 3).所以,大的类过驱动电压将提高MOS管的特征频率fT, 但同时也会增加功耗(对于产生同样的gm来说,大的V*,将要求大的ID).为此,本文引入一个描述参数速度效率指标fT*gm/ID.其中,特征频率fT正相关于V*,而电流效率gm/ID负相关于V*. 图 4描述了类过驱动电压与速度效率指标的SPICE仿真结果.由图 4可知,MOS管的类过驱动电压V*=0.2 V时,能兼顾速度和功耗特性.

|

图 4 V*与速度效率指标的关系 |

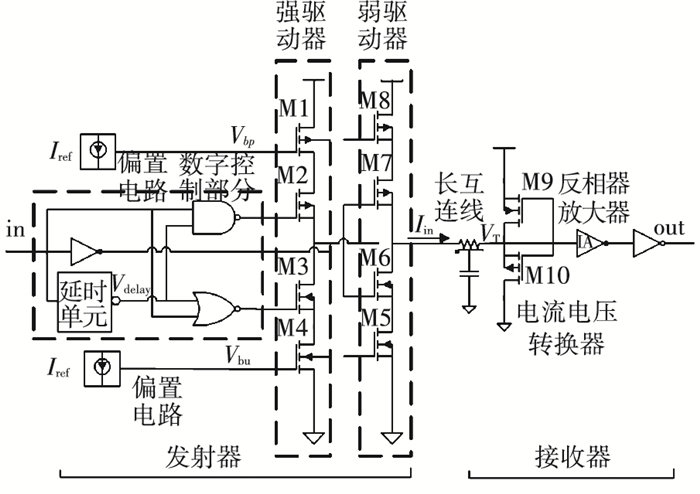

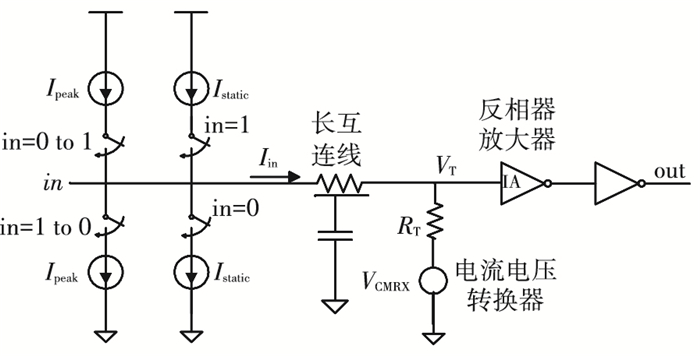

图 5给出了动态电流模式互连电路结构图[15],其由发射器由弱驱动器(weak driver),强驱动器(strong driver),数字控制部分(digital control),以及偏置电路组成,用于将电压信号转换为电流信号注入到长互连线中.接收器由电流电压转换器IVC,反相器放大器IA,反相器组成,用于将电流信号恢复成电压信号.它的等效电路如图 6所示[15],偏置电路用于产生一个参考电流Iref,其镜像产生强驱动电流Ipeak和弱驱动电流Istatic.

|

图 5 动态强驱动电流源结构的电流模互联电路 |

|

图 6 电流模互联电路等效电路 |

弱驱动器在信号传递期间一直工作,当输入信号为1时,M7开启,弱驱动电流Istatic注入到长线中;当输入信号为0时,M6开启,反向弱驱动电流-Istatic注入到长线中.弱驱动电流通过电流电压转换器产生一个低摆幅电压ΔV=2Istatic×RT,其中

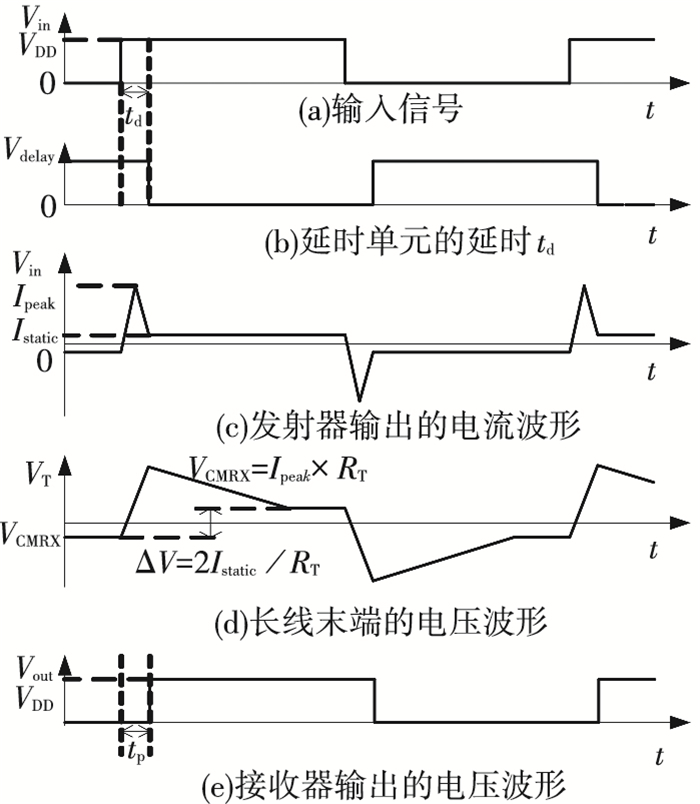

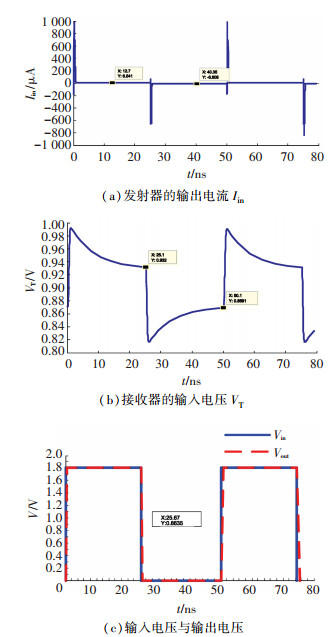

当输入信号为周期性方波时,动态驱动电流模式互连电路的各点波形如图 7所示.其中td表示延时单元的延时;Ipeak,Istatic分别表示强驱动电流和弱驱动电流大小;VCMRX表示电流电压转换器的等效电压源电压. ΔV表示由弱驱动电流造成的电压摆幅. tp表示电压信号经过发射器,长互连线,接收器的传递时间(propagation time).

|

图 7 当输入信号为周期性的方波时该电流模电路各点波形 |

电流模电路整体的平均功耗主要与Ipeak,Istatic和td有关.在满足传递时间的要求下,它们的不同取值产生的功耗也不一样.

Istatic的大小,实际上是由ΔV和RT决定的.为了获得较高的稳定性和噪声容限,所需的ΔV越大,则要求Istatic越大,功耗越大.根据文献[4]所述,其最少为60 mV.此时,若RT越大, 则Istatic越小.取VCMRX=0.9 V(1.8 V的供电电压),则M9和M10的宽长之比一定,又由于电流电压转换器对管子的本征增益无要求,取两个管子的长度L=180 nm,则W9/W10的比值确定.另一方面,M9和M10构成的电流电压转换器的输入电阻为

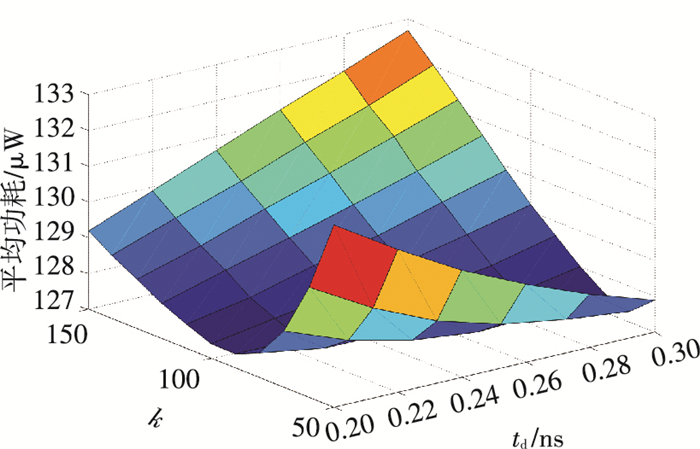

Istatic的选取实际是由电路的稳定性决定,在满足稳定性的前提下,选取最小的Istatic.相比之下,td和Ipeak的选取则由信号的传递延时时间tp和整体功耗的大小决定.当越大,则tp越小,功耗越大;当td和Ipeak过小,强驱动的作用未能发挥,则电流电压转换器处的波形变换缓慢,造成接收器中,各部分充放电时间过长,则整体电路的平均功耗也将上升.综上分析,可知在满足tp的条件下,有最优的td和Ipeak取值.

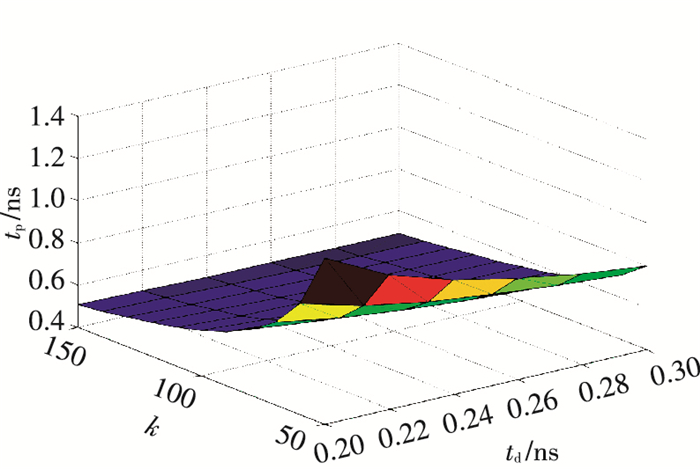

本文用发射器的开关电流源模型对发射器进行建模,其电压输出波形如图 7(c)所示.根据前文分分析取Istatic=6.34 μA.定义

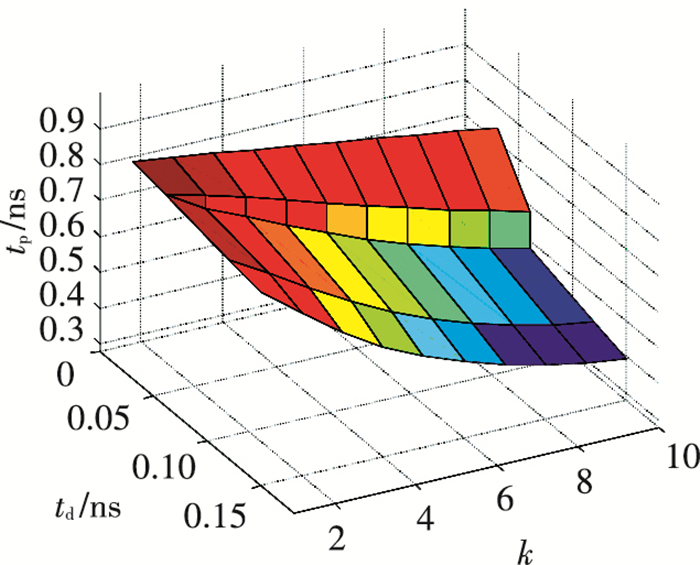

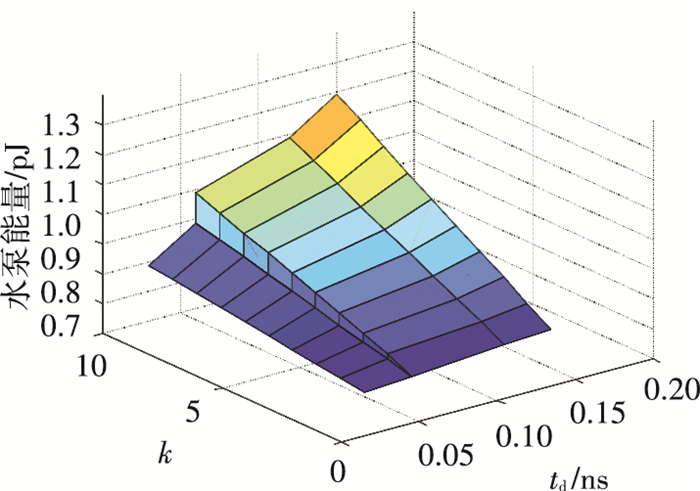

对k和td在一定范围内扫描,在每一对k和td的取值下,进行瞬态仿真,然后让仿真器测量信号的传递时间tp和平均功耗.最后用MATLAB作出tp对k和td,以及平均功耗对k和td的三维图,如图 8、9所示. 图 8显示,对于相同的强驱动电流作用时间td来说,k越大则tp越小.和前面分析一样,图 9显示平均功耗是一个凹面图,有功耗最低点.对于相同td来说,k越大,强驱动电流越大,功耗越大.但是如果k过小时,强驱动作用不明显,接收器各部分充放电时间过长,接收器将消耗大量能量,使得电路整体平均功耗依然上升. 图 8、9可用作动态驱动电流源电流模电路设计指导用表.先在图 8中找到满足信号传递时间tp的k和td的范围,再在图 9中找到使功耗最低的k和td的取值后求交集.当k=100,td=0.28 ns时,tp=0.57 ns最低平均功耗为112 μW.上述结果为该电流模电路本征最低平均功耗.

|

图 8 信号传递时间tp与k和td的关系 |

|

图 9 平均功耗与k和td的关系 |

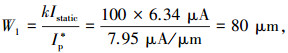

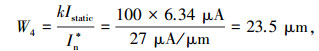

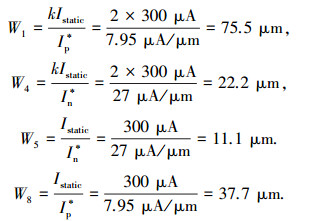

接下来,本文将采用2ID/gm的方法来确定MOS管宽度.为了使MOS管的速度效率指标最高,取M1, M4, M5, M8的类过驱动电压为200 mV,则根据式(5)扫I*与V*的关系得到每单位宽度电流In*= 27 μA/μm,Ip*=7.95 μA/μm,则相应MOS管宽度分别为

|

(6) |

|

(7) |

|

(8) |

|

(9) |

开关管M2, M3, M6, M7的宽度可在M1, M4, M5, M8基础上,按一定比例缩小,保证开关管导通时,电流源管M1, M4, M5, M8工作在饱和区.较小尺寸的驱动管,其自身的寄生电容也较小,有利于节省功耗.

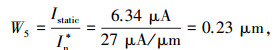

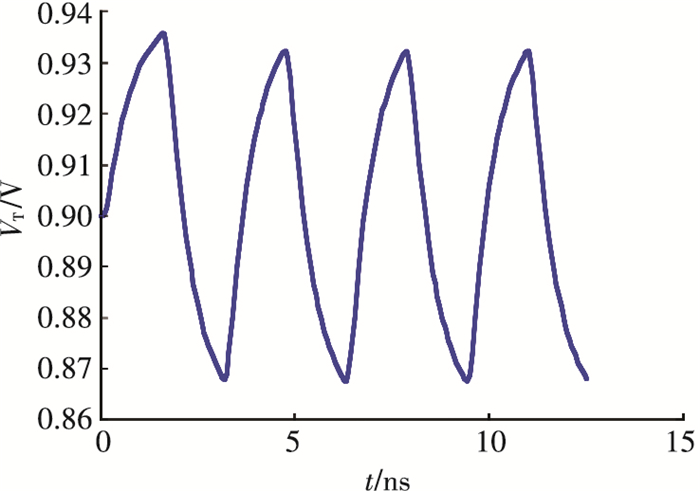

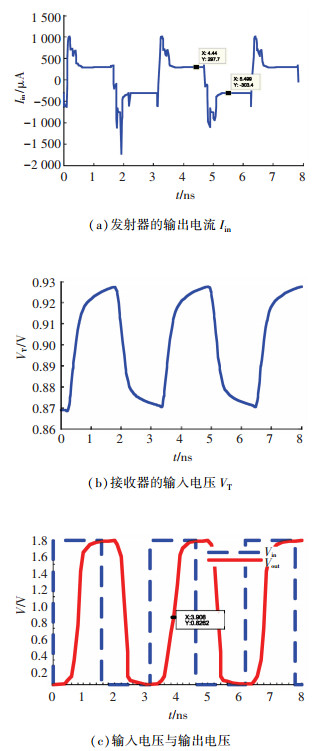

图 10为实际瞬态仿真结果:a)发射器的输出电流,弱驱动电流为6.5 μA, 和计算值6.34 μA非常接近;强驱动电流,与计算值也非常接近,这充分证明了采用2ID/gm方法的优越性;b)接收器的输入电压VT, 其中ΔV=60 mV满足设计要求;c)显示了输入信号和输出信号的传递延时tp约为0.6 ns,接近设计指标0.57 ns.实际仿真测量功耗为121 μW,功耗增加部分主要是偏置电路的功耗.

|

图 10 初次仿真结果 |

在2.2节的优化设计中,定义出了最小的弱驱动电流Istatic=6.34 μA,在输入信号频率低于40 MHz(周期25 ns)时,随着工作频率升高,这样低的弱驱动电流便不能使得在半周期内,VT从870 mV升到930 mV或从930 mV降低到870 mV.于是,在已知信号输入频率范围内,确定最小的Istatic,需要采用新的方法.文献[15]中用的测试信号是由环形振荡器产生的320 MHz周期性方波,用以模拟0.64 Gbps的数据率.本文在这一节中也令输入信号为320 MHz的周期性方波,在此基础上进行功耗优化设计分析.为了确定出在320 MHz工作频率下的最小Istatic,将对图 5重新建模.发射器部分先让强驱动器停止工作,只保留弱驱动器.接收器部分的电流电压转换器,用0.9 V的直流电源加上电阻RT= 30 mV/Istatic.在一定范围内慢慢增加Istatic观察输出波形,直到在半个周期1/640 MHz内,Istatic能使得VT从870 mV升到930 mV, 以及从930 mV降低到870 mV.

图 11给出当Istatic增大到300 μA时,接收器的输入电压摆幅能在1/640 MHz时间内变化60 mV.此时信号传递时间tp约为1 ns,满足时序要求.确定出工作频率在320 MHz下所需的最小Istatic后,接着需要确定出最好的k和td值,以便在满足tp的要求下,功耗最小.同样,将在一定范围内扫描k和td,作出tp与k和td以及能量每位(energy per bit)与k和td的关系,如图 12、13所示(采用的描述功耗的指标是能量每位(energy per bit),它等于功耗除以数据率0.64 Gbps).由图 12、13可知,td=0.06 ns,k=2时,tp约为0.86 ns,能量每位约为0.70 pJ.

|

图 11 输入为320 MHz的弱驱动电流时,接收器的电压波形 |

|

图 12 工作频率为320 MHz时,tp与k和td的关系 |

|

图 13 工作频率320 MHz时,消耗能量与k和td的关系 |

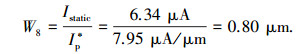

基于2ID/gm的方法求的相应MOS管宽度W为

|

图 14(a)是使用2ID/gm方法计算MOS管尺寸得到的仿真结果.其中Istatic的大小,非常接近设计指标,但是Ipeak有一定偏离,这主要是由于强驱动电流开启时间短,强驱动电流达到设计值需要时间. 图 14(b)显示了接收器端的输入波形,由于强驱动电流的作用,与图 11相比,波形上升速度更快. 图 14(c)显示了输入信号和输出信号对比.经测试,该电路的信号传递时间约为0.79 ns,能量每位约为0.72 pJ.

|

图 14 初次仿真结果 |

由仿真结果可知,先对电流模电路采用行为级建模,确定出最优的td,Ipeak,Istatic的值,再用2ID/gm的方法确定出具体MOS管的尺寸,与设计指标十分相近.因此,这种自顶向下设计方法,能够非常迅速地完成电流模电路设计,并且可用于其他模拟集成电路的快速设计中.

3 结论1) 针对动态驱动电流模电路提出了一种新的自顶向下的功耗优化设计方法.通过MATLAB对仿真数据进行处理,找到所需的最优电流大小.基于2ID/gm确定动态驱动的电流模电路中所有MOS管的尺寸.

2) 通过对动态驱动电流模电路的本征功耗优化和固定工作频率下的功耗优化设计和仿真分析,结果表明,该方法确定的MOS管仿真初值非常接近设计指标,大大提高了设计效率.这种自顶向下的设计方法也能有效地用于其他模拟集成电路的快速设计中.

| [1] |

SEO S J, HO R, LEXAU J, et al. High-bandwidth and lowenergy on-chip signaling with adaptive pre-emphasis in 90nm CMOS[C]//IEEE ISSCC Dig Tech Papers. San Francisco: IEEE, 2010. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5433993

|

| [2] |

MENSINK E, SHINKEL D, KLUMPERINK E A M, et al. Power efficient gigabit communication capacitively driven RC-limited on-chip interconnects[J]. IEEE J Solid-State Circuits, 2010, 45(2): 447-457. DOI:10.1109/JSSC.2009.2036761 |

| [3] |

DAVE M, SHOJAEI M, SHARMA D. Energy-efficient current-mode signaling scheme for on-chip interconnects[C]//Asian Solid-State Conf. Beijing: IEEE, 2010.

|

| [4] |

DAVE M, JAIN M, BAGHINI M S, et al. A variation tolerant current-mode signaling scheme for on-chip interconnects[J]. IEEE Trans Very Large Scale Inter (VLSI) Syst, 2013, 21(2): 342-353. DOI:10.1109/TVLSI.2012.2185835 |

| [5] |

KATOCH A, VEENDRICK H, SEEVINCK E. High speed current-mode signaling circuits for on-chip wires[C]//IEEE Int Symp Circuits Syst. Kobe: IEEE, 2005. http://ieeexplore.ieee.org/iel5/9898/31469/01465542.pdf

|

| [6] |

SHINKEL D, MENSINK E, KLUMPERINK E A M, et al. A 3-Gb/s/ch transceiver for 10-mm uninterrupted RC-limited global on-chip interconnects[J]. IEEE J Solid-State Circuits, 2006, 41(1): 297-306. DOI:10.1109/JSSC.2005.859880 |

| [7] |

ZHANG L, WILSON J, BASHIRULLAH R, et al. A 32 Gb/s on-chip bus with driver pre-emphasis technique for on-chip buses[C]//Proceeding of Custom Integr Circuits Conf(CICC). San Jose: IEEE, 2006.

|

| [8] |

TABRIZI M M, MASOUMI N, DEILAMI M M. High speed current-mode signalling for interconnects considering transmission line and crosstalk effects[C]//Proceeding of MWCAS. Montreal: IEEE, 2007. http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4488531

|

| [9] |

HO R, ONO T, HOPKINS R D, et al. High speed and low energy capacitively driven on-chip wires[J]. IEEE J Solid-State Circuits, 2008, 43(1): 52-60. DOI:10.1109/JSSC.2007.910807 |

| [10] |

SILVEIRA F, FLANDRE D, JESPERS P G A. A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on insulator micro-power OTA[J]. IEEE J Solid-State Circuits, 1996, 31(9): 1314-1319. DOI:10.1109/4.535416 |

| [11] |

FOTY D, BUCHER M, BINKLEY D. Re-interpreting the MOS transistor via the inversion coefficient and the continuum of gms/Id[C]//Proceeding of Int Conf on Electronics, Circuits and Systems. Dubrovnik: IEEE, 2002. http://ieeexplore.ieee.org/iel5/8101/22424/01046463.pdf

|

| [12] |

BOSER B E. Analog circuit design with submicron transistors[EB/OL]. (2014-12-20)[2015-03-03]. http://www.ewh.ieee.org/r6/scv/ssc/May1905.htm.

|

| [13] |

JESPERS P. The gm/ID methodology a sizing tool for low-voltage analog CMOS circuits[M]. New York: Springer, 2010: 74-100.

|

| [14] |

KONISHI T, INAZU K, LEE J G, et al. Optimization of high-speed and low-power operational transconductance amplifier using gm/ID lookup table methodology[J]. IEICE Trans Electronics, 2011, E94.C(3): 334-335. DOI:10.1587/transele.E94.C.334 |

| [15] |

WANG X, HU Y, HAN L, et al. A low power and variation insensitive current mode signaling scheme[J]. Journal of Circuits Systems and Computers, 2013, 22(8): 124. |

2016, Vol. 48

2016, Vol. 48