2. 中国科学院大学, 北京 100190

2. University of Chinese Academy of Sciences, Beijing 100190, China

随着航空航天事业的快速发展,空间探测器的有效载荷种类及任务形式多样化,对星上数据管理系统高速并行存储能力提出更高要求.星载存储器是数管系统的核心设备之一[1-2].基于NAND Flash的固态存储器具有存储密度高、非易失等特点,是星上数据存储的主流方式[3-5].

目前星载存储器方案主要面向低速有效载荷设计,支持信源量小、固定分区存储灵活性差[6-7],如暗物质粒子探测卫星、实践十号科学实验卫星存储器有效吞吐率低于350Mbps,仅支持两路数据分区存储,无法适用于多路载荷数据高速输入、同一时刻多任务等工作模式.徐永刚等[8]基于Flash设计的图像记录系统使用CPU内存作为两路外部图像数据缓存,每路各缓存一幅图像后由CPU将数据按顺序逐一写入Flash阵列中,其缓存调度方式制约了载荷数据的输入速率.李晴等[9-10]针对Flash存储技术和高速互连技术进行了研究,系统通过多个存储体同时工作实现对多种类型数据记录,虽然提高了系统存储吞吐率,但不支持单个存储体对多路载荷数据的有效存储,无法适用于对功耗、重量等要求严格的航天领域.为此,针对星载存储器实际应用,对固态存储器吞吐率瓶颈进行分析,探讨提高吞吐率关键技术以支持高速载荷数据输入,并对高速并行缓存与任务调度机制进行设计验证,以期解决单板存储器对多路高速数据同步缓存与自主存储方案的需求问题.

1 星载存储器吞吐率分析 1.1 基于Flash存储器吞吐率瓶颈目前星载存储器主要使用经抗辐照加固处理后的宇航级3DFN64G08VS NAND Flash叠装芯片,每个叠装模块由8片K9F8G08U0M基片组成[11].设叠装模块Flash数据总线位宽为Wone_die,最大工作频率为fflash_work_max,则单个模块理论最高吞吐率为

| $ {H_{{\rm{one\_die\_theory\_max}}}} = {f_{{\rm{flash\_work\_max}}}}*{W_{{\rm{one\_die}}}}. $ | (1) |

宇航级NAND Flash基片最高工作频率为50 MHz,抗辐照加固后叠装模块最高工作频率降为40 MHz.根据军用元器件80%降额使用准则,NAND Flash实际最高工作频率为32 MHz,又Wone_die=8bit,由式(1)可得Flash叠装模块理论最高吞吐率为256 Mbps.

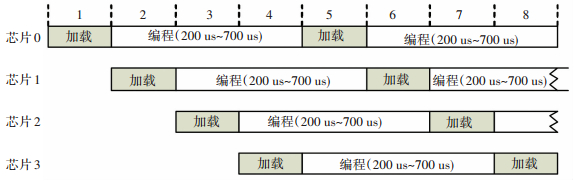

固态存储器的固有写操作特性降低了有效吞吐率. K9F8G08U0M基片以页为单位进行读写操作,一页数据区大小为4 096 Bytes,数据写入时,先将数据加载到芯片内部缓存区,再经过编程完成数据写入,写操作流程见图 1.

|

图 1 NAND Flash写操作流程 Figure 1 Procedure of NAND Flash writing operation |

根据写操作时序要求,完成一页数据写操作需要的时间为:

| $ {t_{{\rm{one\_page\_write}}}} = {t_{{\rm{LOAD}}}} + {t_{{\rm{PROG}}}} + {t_{{\rm{CHECK}}}}, $ | (2) |

| $ {t_{{\rm{LOAD}}}} = {t_{{\rm{command}}}} + {t_{{\rm{address}}}} + {t_{{\rm{ADL}}}} + {t_{{\rm{data}}}}. $ | (3) |

时序参数见表 1,其中:T为时钟周期,None_page为页容量,tWHR为读取编程结果等待时间.

| 表 1 Flash写操作时序参数表 Table 1 Timing parameter of Flash writing operation |

设Flash有效写操作效率为ηone_die_write,实际工作时最大支持写速率为Hone_die_theory_max,则

| $ {\eta _{{\rm{one\_die\_write}}}} = \frac{{{T_{{\rm{WC}}}}*{N_{{\rm{one\_page}}}}}}{{{t_{{\rm{one\_page\_write}}}}}}, $ | (4) |

| $ {H_{{\rm{one\_die\_work\_max}}}} = {H_{{\rm{one\_die\_thy\_max}}}}*{\eta _{{\rm{one\_die\_write}}}}. $ | (5) |

由式(2)~(5)可得Flash在实际工作中的最高有效写操作效率为38.97%,最高写速率为99.76 Mbps,无法满足多路高速载荷数据的存储需求.

1.2 提高吞吐率关键技术 1.2.1 流水线操作在Flash写操作流程中,芯片编程占用大量时间,大大降低了Flash的写入效率,采用流水线操作方式可解决芯片内部编程过程中的长时间等待问题.流水线写Flash操作原理见图 2.

|

图 2 四级流水线加载Flash原理 Figure 2 Four-level pipeline load operation of NAND Flash |

每次加载数据到一组Flash芯片后,该组芯片进入内部编程状态,在此期间尽管不能对该组芯片进行其它操作,但可立即进行另一组芯片加载.由芯片加载时间与编程时间数值关系知,当第4组芯片加载完毕后,第1组芯片的编程过程通常已经结束.使用四级流水线操作技术,可以基本保证宏观上实现对存储区的全速率无间断数据写入,Flash有效写操作速率接近理论值256 Mbps,解决了存储介质固有写操作特性对存储器有效吞吐率的限制.

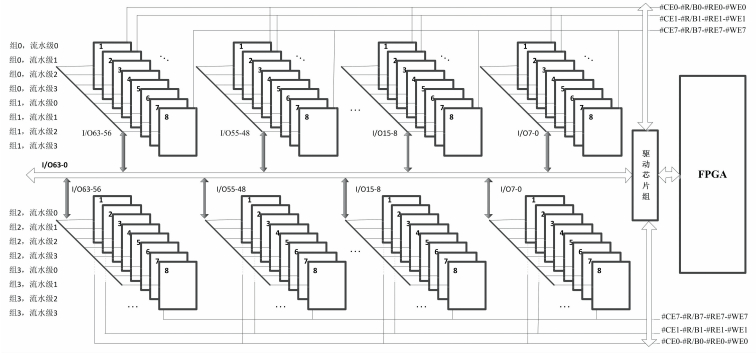

1.2.2 总线并行扩展为进一步提高存储吞吐率,扩展存储容量,在空间横向轴上采用I/O总线并行扩展技术.综合考虑FPGA管脚资源和存储器性能需求,设计8倍I/O总线并行扩展方案,并行扩展结构见图 3.

|

图 3 8倍FLASH I/O并行扩展结构图 Figure 3 8 times parallel I/O bus expansion of NAND Flash |

将8片Flash叠装模块控制总线、状态总线互连,而I/O总线扩展为64位,64位总线不同数据位段分别对应8片并行扩展的Flash的8位总线,将Flash中8片并行的页扩展成1簇进行读写操作.由于物理空间扩展与芯片操作时序无关,因此8倍总线扩展后系统速率将提高为原来的8倍,此时存储器单板理论可支持最高2Gbps数据输入,提高了存储系统对高速载荷数据的吞吐能力.

2 高速缓存与存储任务调度四级流水线的操作特点要求Flash在启动写操作时,将加载所需的四簇数据准备完成,以确保四级流水加载连续性,同时为保证每次流水操作均是针对同一载荷,需设计并行缓存机制解决多路载荷数据各自分区缓存问题.

传统方案使用FPGA内部双端口RAM作为缓存以降低控制复杂度,但对于多路载荷高速并行输入,有限的RAM资源难以满足缓存容量需求.外置缓存芯片SRAM虽然有了一定容量提升,但仍然有限,并且在64位数据总线下SRAM接口速率最高为2 Gbps,数据吞吐复用I/O端口时平均读写速率只有1 Gbps,限制了Flash最高写速率使用.宇航级SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存储器)芯片最高工作频率达133 MHz,当数据总线为64 bits时,理论接口总吞吐率可高达8 Gbps,且芯片容量3 Gbits,能够满足系统高吞吐率需求.

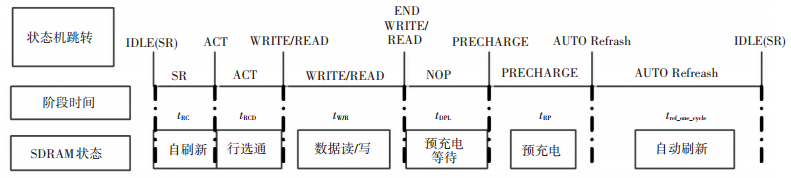

2.1 SDRAM缓存可行性SDRAM芯片一次完整的读/写数据操作包括自刷新、行选通、数据突发读写、预充电及自动刷新等部分[12],操作流程见图 4.

|

图 4 SDRAM读写操作流程图 Figure 4 Procedure of SDRAM reading/writing operation |

SDRAM换行操作需再次行选通,为减小时间开销,设计一次读、写所涉及地址均在同一行内,数据吞吐采用8字突发传输方式.由于SDRAM芯片每64 ms内必须完成8 192次自动刷新操作以保证数据有效,为保证连续读/写作过程满足刷新要求,将自动刷新机制分配到每个读/写周期操作后,此时

| $ \begin{array}{l} {H_{{\rm{W/R\_operate}}}} = \frac{{{N_{{\rm{W/R}}}}*T*{W_{{\rm{data\_bus}}}}*\left( {1/T} \right)}}{{{t_{{\rm{RC}}}} + {t_{{\rm{RCD}}}} + {N_{{\rm{W/R}}}}*T + {t_{{\rm{DPL}}}} + {t_{{\rm{RP}}}} + {N_{{\rm{ref}}}}*{t_{{\rm{RC}}}}}}\\ {t_{{\rm{RC}}}} + {t_{{\rm{RCD}}}} + {N_{{\rm{W/R}}}}*T + {t_{{\rm{DPL}}}} + {t_{{\rm{RP}}}} + {N_{{\rm{ref}}}}*{t_{{\rm{RC}}}} \le \frac{{{t_{{\rm{REF(max)}}}}}}{{{N_{{\rm{cycles}}}}}}. \end{array} $ | (6) |

其中:NW/R为一个读/写周期的数据大小,T为SDRAM工作时钟周期,Nref为每次读/写操作后自动刷新次数,操作时序参数见表 2.

| 表 2 SDRAM时序参数 Table 2 Timing parameter of SDRAM operation |

当SDRAM工作时钟为64 Mhz,Nref取2时,由式(6)可得吞吐率HW/R_operate=3.848 Gbps,平均读写速率HW/R_operate_average=1.924 Gbps,与NAND Flash最大支持写速率相匹配,能够满足多通道分区输入速率、空间需求,缓存方案可行.

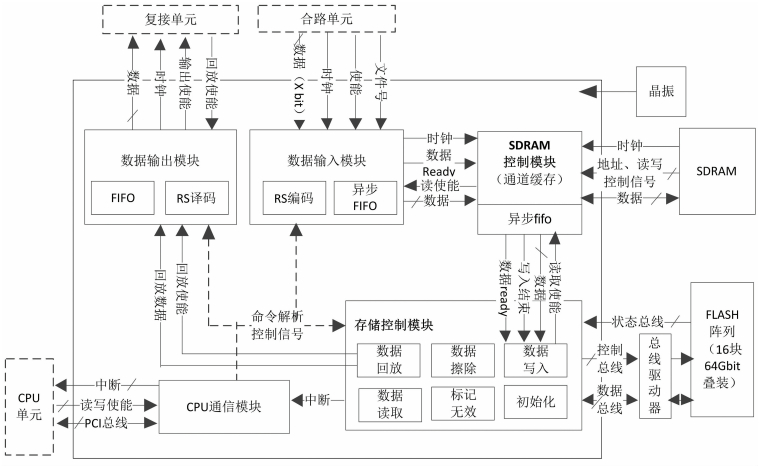

2.2 星载存储器方案设计采用四级流水线操作与总线并行扩展技术提高单板存储吞吐率与存储容量,采用SDRAM芯片作为缓存支持高速并行数据输入,星载存储器总体设计方案见图 5.

|

图 5 星载存储器方案框图 Figure 5 Diagram of spaceborne storage system |

新型星载存储器设计参数为单板数据吞吐率2 Gbps,存储容量1 Tbits.采用FPGA作为控制器载体,配置SDRAM高速并行缓存,将各载荷数据动态自主存储于NAND Flash中.数管系统CPU单元运行存储管理软件,实现存储系统的文件化管理.

2.3 高速数据并行缓存在多路高速载荷数据并行输入的工况下,合路单元设置FIFO分别接收缓存,同时设定文件号与之对应.随后数据被送至存储控制单元,经RS(252,256)纠错编码后通过双FIFO进行乒乓缓存.任一FIFO缓存满256字后向SDRAM控制模块发出读申请,SDRAM根据载荷数据文件号将数据送往对应的分区通道进行缓存.当任一SDRAM分区内缓存的数据量满足四级流水需要(即满4簇)时,存储控制FPGA与CPU单元协同管理,启动Flash写操作,将数据按四级流水写入固态存储介质.多通道数据并行接收与缓存流程见图 6.

|

图 6 多通道数据并行接收与缓存流程图 Figure 6 Parallel reception and cache of multi-channel data |

由于各载荷通道数据速率的差异,导致SDRAM各分区内缓存数据量互不相同,当多个缓存通道同时满4簇大小,或者一个缓存通道中有多个4簇大小缓存时,可通过通道缓存任务调度机制保证数据被完整有效存储.

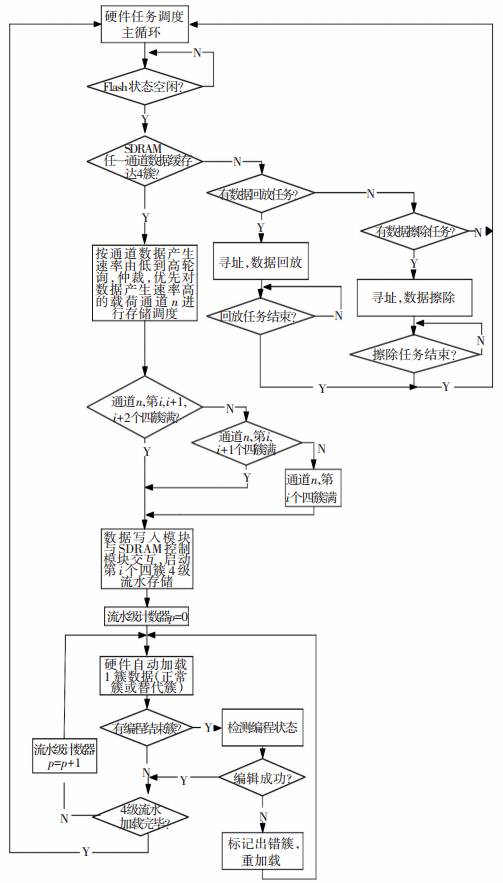

设计Flash写操作优先级最高,读操作次之,擦除操作优先级最低,以保证Flash在复杂工况下载荷数据被优先存储;设计优先对SDRAM通道缓存中速率高的载荷数据进行写Flash操作,以防止数据缓存溢出.通道缓存任务调度与存储流程见图 7.

|

图 7 通道缓存任务调度与存储流程图 Figure 7 Channel cache task scheduling and storage process |

存储控制FPGA根据载荷数据产生速率高低由小到大依次分配文件号,SDRAM控制模块按文件号由大到小轮询各通道数据缓存情况,当某通道缓存数据多于4簇时,寄存该通道文件号.完成所有通道遍历后,确定当前被操作通道,如果被操作缓存通道有多个4簇数据,则按缓存时间先后顺序进行通道内各4簇数据调度读取.

SDRAM各通道需设置的缓存空间大小由多路有效载荷数据速率综合决定.保证通道缓存不溢出的条件是存储器在极限工况下工作时SDRAM各通道仍有缓存空间,即在SDRAM各缓存通道都即将满4簇时,NAND Flash启动了擦除操作,待擦除操作完成后,所有通道缓存数据被完整写入Flash存储区.

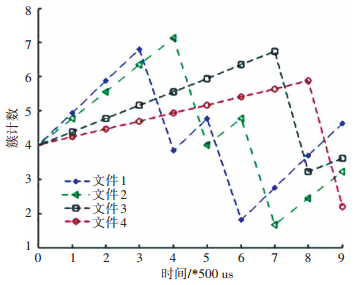

3 仿真验证为验证存储器高速并行缓存与任务调度机制设计正确性,使用Matlab工具进行模型仿真.设置输入条件为:1)4路载荷,数据速率分别为480 Mbps、400 Mbps、200 Mbps、120 Mbps;2)文件号对应设定为1~4;3)极限工况;4)载荷数据连续输入;5)Flash擦除时间1.5 ms,流水写4簇数据时间0.5 ms;6)存储无失败.对SDRAM内部各文件缓存变化情况进行仿真观察,结果见图 8.

|

图 8 4路文件并行缓存与存储调度模型仿真 Figure 8 Model simulation of 4 files parallel cache and storage scheduling |

t=0时刻,4路文件缓存均将满4簇,由于擦除任务阻塞,Flash不执行写操作;

t=0~3时,Flash擦除操作,4路文件持续写入SDRAM缓存,无写Flash操作;

t=3时刻,Flash擦除结束,4路文件缓存均多于4簇,根据优先级读文件1缓存写Flash;

t=4时刻,文件1写结束,文件2、文件3、文件4缓存多于4簇,读文件2缓存写Flash;

t=5时刻,文件2写结束,文件1、文件3、文件4缓存多于4簇,开始读文件1写Flash;

t=6时刻,文件1写结束,文件2、文件3、文件4缓存多于4簇,开始读文件2写Flash;

t=7时刻,文件2写结束,文件3、文件4缓存多于4簇,开始读文件3写Flash;

t=8时刻,文件3写结束,文件4缓存多于4簇,开始读文件4写Flash;

t=9时刻,因擦除阻塞累积的所有缓存文件全部写入Flash中,SDRAM进入常规动态平衡调度状态.

综上,在极限工况下4路文件数据被连续并行接收缓存至SDRAM中,并按照存储优先级动态自主调度写入Flash,期间缓存无溢出,并最终进入常规动态平衡调度状态.仿真结果符合并行缓存与任务调度机制设计,满足了多路高速数据同时输入需求,说明方案机理设计有效可行.

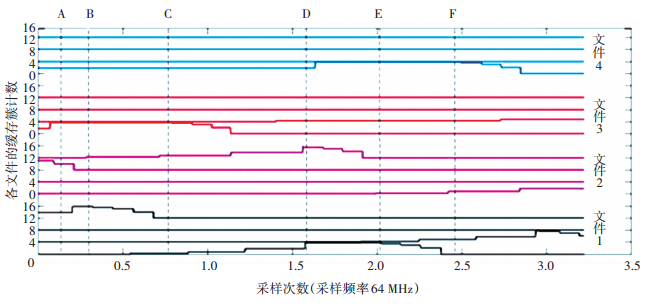

为进一步验证高速并行缓存与任务调度机制的实用性,基于FPGA开发程序进行原型功能仿真.参考模型仿真结果,并考虑到FPGA内部模块间交互时间开销与Flash可能存储失败重加载的影响,设置各文件缓存通道大小为4个4簇(0~3,4~7,8~11,12~15).在与模型仿真实验相同载荷速率输入条件下,4路文件并行缓存与存储调度原型功能仿真结果见图 9.

|

图 9 4路文件并行缓存与存储调度原型功能仿真 Figure 9 Prototype function simulation of 4 files parallel cache and storage scheduling |

在原型功能仿真结果中选取部分关键时间点,观察分析SDRAM内各文件缓存调度变化情况见表 3.

| 表 3 原型功能仿真中各文件缓存与存储调度情况 Table 3 Caching and storage scheduling status of files in prototype function simulation |

由原型功能仿真结果可知,在实际工作中4路载荷文件被并行接收缓存至SDRAM中,存储任务调度机制根据各分区缓存状态将文件按优先级自主动态写入Flash中,仿真结果与模型仿真结果吻合,并验证了存储器单板可有效支撑1.2Gbps数据输入,证明了高速并行缓存与任务调度方案的可行性和实用性.

4 结论针对目前星载存储器无法有效支持多路高速数据并行存储的问题,采用四级流水线操作和总线并行扩展方案,提高了存储系统对多路高速数据的存储能力;设计SDRAM高速多通道缓存与存储协同调度机制,实现了多路数据有效并行接收缓存与存储,确保了复杂工况下数据存储完整性.模型仿真与原型功能仿真结果表明SDRAM高速多通道缓存与存储写操作协同调度机制设计有效可行.

| [1] |

MORGAN P S. Cassini Mission-to-Saturn Spacecraft overview & CDS preparations for end-of-mission Proximal Orbits[C]// 2015 IEEE Aerospace Conference. Big Sky, MT:IEEE Press, 2015:1-18. DOI: 10.1109/AERO.2015.7118911.

|

| [2] |

FABIANO M, FURANO G. NAND flash storage technology for mission-critical space applications[J].

IEEE Aerospace and Electronic Systems Magazine, 2013, 28(9): 30-36.

DOI: 10.1109/MAES.2013.6617096 |

| [3] |

李姗, 宋琪, 朱岩, 等. 星载大容量固态存储器快速可靠启动算法设计[J].

哈尔滨工业大学学报, 2015, 47(10): 1-10.

LI Shan, SONG Qi, ZHU Yan, et al. Design of quick initialization algorithm for space-borne solid state recorder[J]. Journal of Harbin Institute of Technology, 2015, 47(10): 1-10. DOI: 10.11918/j.issn.0367-6234.2015.10.019 |

| [4] |

REID M, OTTMAN G. Software controlled memory scrubbing for the Van Allen Probes Solid State Recorder (SSR) memory[C]// IEEE Aerospace Conference. Big Sky, MT:IEEE Press, 2014:1-6. DOI: 10.1109/AERO.2014.6836406.

|

| [5] |

KIM J Y, PARK S H, SEO H, et al. NAND flash memory with multiple page sizes for high-performance storage devices[J].

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24(2): 764-768.

DOI: 10.1109/TVLSI.2015.2409055 |

| [6] |

宋琪. 星载固态存储技术的应用与研究[D]. 北京: 中国科学院大学, 2015.

SONG Qi. Research and application of spaceborne solid state reocorder technology[D]. Beijing: University of Chinese Academy of Sciences, 2015. http://cdmd.cnki.com.cn/Article/CDMD-80073-1015351185.htm |

| [7] |

HSIEH J W, TSAI Y L, KUO T W, et al. Configurable flash-memory management: performance versus overheads[J].

IEEE Transactions on Computers, 2008, 57(11): 1571-1583.

DOI: 10.1109/TC.2008.61 |

| [8] |

徐永刚. 基于NAND Flash的嵌入式图像记录技术[D]. 北京: 中国科学院大学, 2013.

XU Yonggang. Embedded image recording technology based on NAND flash[D]. Beijing: University of Chinese Academy of Sciences, 2013. http://cdmd.cnki.com.cn/Article/CDMD-80151-1013026456.htm |

| [9] |

李晴. 高速大容量NAND FLASH存储系统的设计与实现[D]. 北京: 北京理工大学, 2015.

LI Qing. The design and realization of a high speed and large capacity NAND FLASH storage system[D]. Beijing: Beijing Institute of Technology, 2015. http://cdmd.cnki.com.cn/Article/CDMD-10007-1015029876.htm |

| [10] |

徐玉杰. 高速大容量存储系统的设计与实现[D]. 西安: 西安电子科技大学, 2014.

XU Yujie. Design and implementation of high-speed and huge-capacity storage system[D]. Xi'an: Xidian University, 2014. http://cdmd.cnki.com.cn/Article/CDMD-10701-1014327935.htm |

| [11] |

Samsung Electronics. K9F8G08UXM NAND FLASH memory data sheet[EB/OL].(2007-3-31). www.datasheetspdf.com/datasheet/K9F8G08UXM.html.

|

| [12] |

Orbita Control Engineering Co., Ltd. VDSD3G48XQ114XX6V75 user manual(Version 1.4)[EB/OL].[2016-11-29]. www.myorbita.net.

|

2017, Vol. 49

2017, Vol. 49