随着诸如医疗电子、无线传感节点等应用的兴起,低功耗芯片受到了越来越广泛的关注.这类芯片对性能要求不高,但对功耗要求苛刻.静态随机存储器 (SRAM) 作为芯片的重要组成部分,大程度上影响着芯片的面积和功耗,因此其功耗的优化成了芯片功耗优化的关键所在.当电压在亚阈值区附近时,SRAM会出现最优能耗点[1].然而,亚阈值电压下,常规6管单元的噪声容限和读写能力会严重恶化,导致SRAM不能工作.所以,设计者提出了各种新的单元和外围电路结构.新型的单元结构,比如8管单元[2-5],9管单元[6]和10管单元[7-9],通过加入额外的晶体管将读写操作分离,使SRAM能工作在亚阈值区.然后再对单元进行尺寸调整以增大噪声容限和读写能力,使SRAM在亚阈值区的工作状态更加稳定.但是传统的尺寸调整法在亚阈值区存在面积开销过大的问题, 为缓解该问题,一些辅助的外围电路技术被提了出来.例如,虚地技术[6, 8-10]和虚电源技术[10]可以在付出较小单元面积的代价下,保证亚阈值区性能.然而,这些技术不仅导致了额外的外围电路开销,同时也引起了单元稳定性恶化等问题.

本文针对传统方法在改善亚阈值区SRAM性能上存在的局限性,提出了利用亚阈值区晶体管的反短沟效应和反窄沟效应去提升SRAM性能的方法,从而避免了不必要的面积和电路开销.同时将上述方法应用在亚阈值单元的尺寸设计上,测试结果表明, 该方法有效地提升SRAM的噪声容限,并且加强其读写能力,在付出较小的代价下保证了SRAM在亚阈值区的性能.

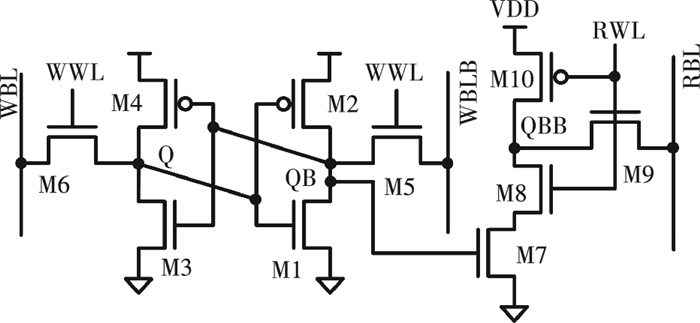

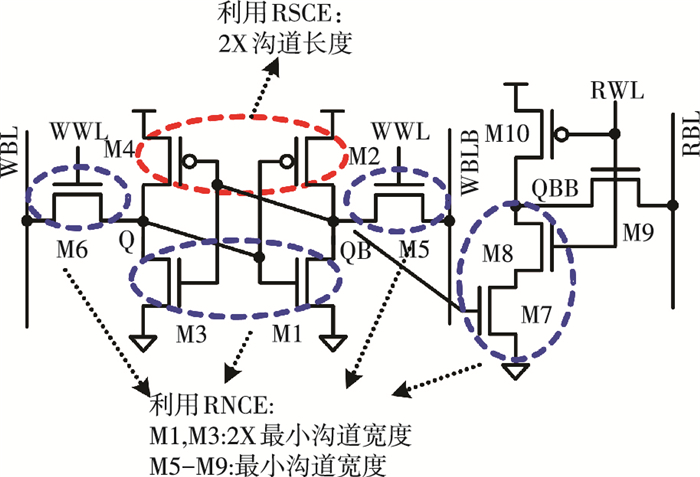

1 提升SRAM单元性能的传统方法 1.1 设计采用的单元结构图 1是设计中的10管SRAM单元,包含3个组成部分:两个背靠背反相器组成的反馈环电路 (M1, M2, M3, M4),两个存取晶体管 (M5, M6) 组成的写入晶体管对,一个读出电路 (M7, M8, M9, M10).当对单元进行写操作时,写字线WWL被使能 (M5和M6开启),写位线上的数据可以灌入反馈环电路中,从而改写内部数据.当进行读操作时,读字线RWL被使能,读位线RBL的电平会随着内部存储的数据进行变化.由于此单元隔离了读写操作,使读噪声容限和保持噪声容限大小相同.因此,SRAM噪声容限的优化只需要考虑保持噪声容限.

|

图 1 10管亚阈值SRAM单元 Figure 1 SRAM 10-T cell |

SRAM单元的数据保持功能是通过背靠背的反相器实现的,因此,为了使单元能最稳定地保持数据,每个反相器都要工作在最优的噪声容限下.使单个反相器获得最优噪声容限的传统做法是,先把NMOS和PMOS的沟道长度固定为最小沟道长度,再调整NMOS和PMOS的宽度比 (Wp/Wn),从而匹配两者的驱动能力.

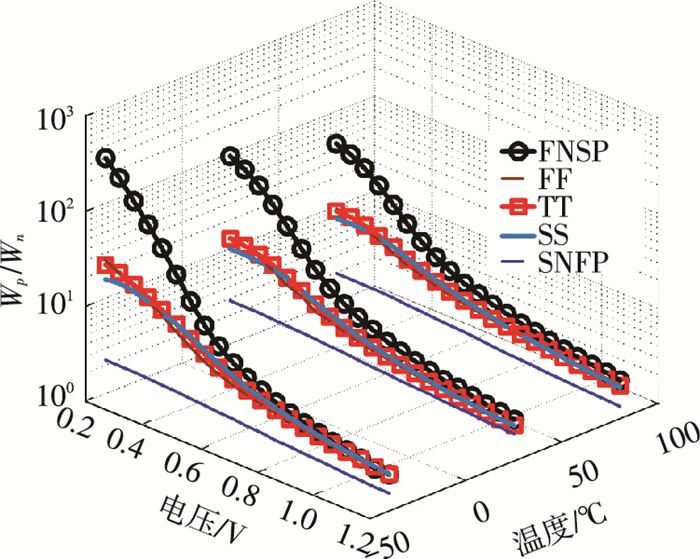

图 2显示了室温下 (25 ℃),传统尺寸调整方法在不同电压下宽度比的变化趋势.从全局观察,宽度比随电压降低呈增长趋势.同时,其增长率在不同工艺角下有明显差别.产生这个趋势的原因在于:PMOS与NMOS驱动能力的差距随电压降低而加大,不同的工艺角又会影响这个差距的数值.最终,低电压下PMOS需要付出不同的面积代价去匹配NMOS的驱动能力.室温下,最恶劣的宽度比出现在电压为0.2 V,工艺角为FNSP的条件下.此时数值为93左右,消耗了大量面积.此外,温度对宽度比也有着不可忽略的影响.引入温度因素后,传统的尺寸调整方法会带来如图 3所示的变化.随着温度的降低 (80 ℃,25 ℃,-40 ℃),尺寸开销加剧.在-40 ℃和80 ℃下,最坏情况依旧出现在0.2 V电压,FNSP工艺角下,此时宽度比分别达到300和45.

|

图 2 室温下宽度比随电压和工艺角的变化趋势 Figure 2 Rate trend with the voltages and corners |

|

图 3 不同温度和工艺角下宽度比的变化趋势 Figure 3 Rate trend in different temperatures and corners |

巨大的尺寸开销不仅会导致漏电的增加,也会影响电路在亚阈值区的功能.而且,由于亚阈值区晶体管电流与阈值成指数关系,所以微小的阈值变化都能带来显著的电流变化,从而导致宽度比发生进一步偏移[11].因此,为维持SRAM单元在亚阈值区的噪声容限,采用传统的尺寸调整法会使得单元的反馈环付出更大的面积代价.

与此同时,单元的写能力受上拉晶体管和存取晶体管的相对强度影响,当使用大尺寸的上拉晶体管 (M2, M4) 时,存取晶体管 (M5, M6) 的尺寸会相应增大以保证写能力,从而又增大了单元面积.因此,许多学者提出了各种方案:比如在存取晶体管上加上高电压的字线电平以增强晶体管的导通能力,或者降低要写入单元的供电电压,使得上拉晶体管的能力变弱,从而降低尺寸开销.但是这两种方法都需要额外的布线开销和供电电路,会产生多余的功耗[11],同时也会影响SRAM阵列中半选单元的稳定性,导致SRAM不能稳定工作.所以,外围辅助电路虽然一定程度上能改善传统尺寸调整方法的劣势,但也会带来电路和功耗开销并导致其他问题的产生.

2 设计中采用的提升亚阈值SRAM单元性能的方法综上分析可知,在亚阈值区,传统的尺寸调整方法会付出很大的面积和电路代价,而且所能获得的降电压空间也不理想.在低电压下晶体管有两种效应:反短沟效应 (RSCE) 和反窄沟效应 (RNCE).将这两种效应应用到单元尺寸的调节上,可以在保证面积开销降低的前提下,有效提高单元的性能.

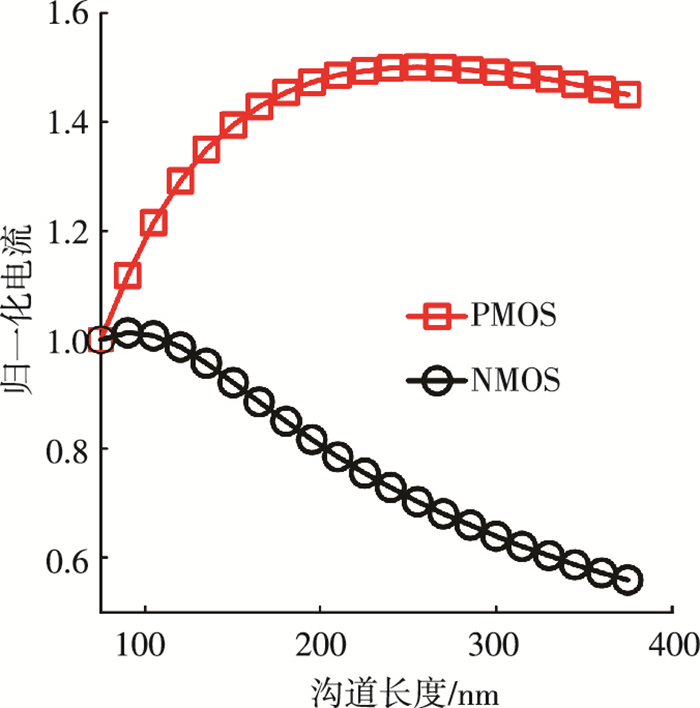

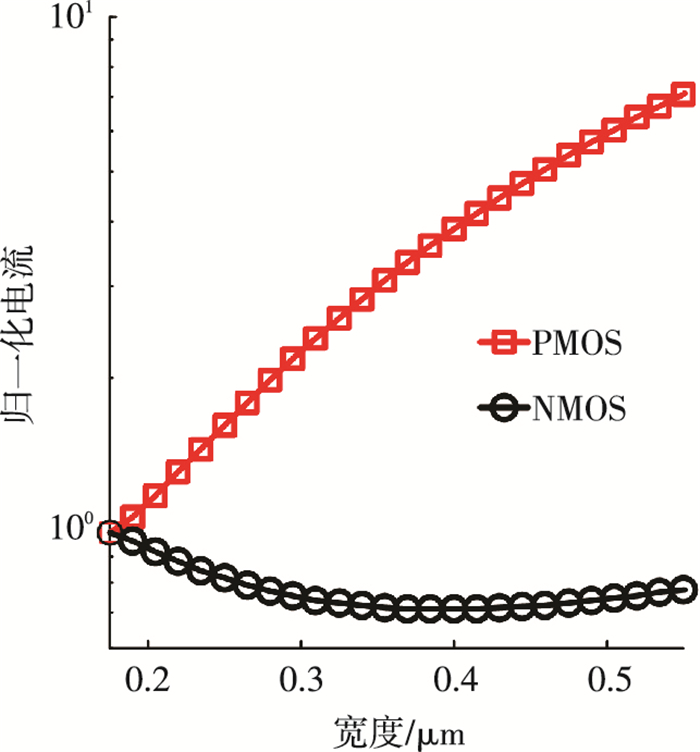

2.1 反短沟效应和反窄沟效应反短沟效应和反窄沟效应的出现归因于晶圆生产过程中采用的HALO技术和STI技术.这两种技术被用以缓和漏感应势垒降低效应 (DIBL).然而,DIBL效应在低电压下会减弱,此时HALO技术和STI技术就会带来反短沟效应[12-13]和反窄沟效应.由于这两个效应在低电压时才会突显,所以传统方法进行尺寸调整时忽略了这两个效应,而本文着重将其引入到晶体管尺寸调整方法中,以达到优化低电压下晶体管尺寸开销的目的.图 4, 5分别为0.3 V电压下反短沟效应和反窄沟效应对晶体管电流的影响.由图 4, 5可知,在一定范围内,PMOS存在明显的反短沟效应,其电流随沟道长度增加而变大;而NMOS存在明显的反窄沟效应,其电流随宽度增加而减小.

|

图 4 反短沟效应对晶体管电流的影响 Figure 4 Reverse short channel effect |

|

图 5 反窄沟效应对晶体管电流的影响 Figure 5 Reverse narrow channel effect |

考虑NMOS和PMOS的反窄沟效应和反短沟效应后,在定宽度比时,相比于传统方法,沟道长度不再固定于最小沟道长度,而是选取一个在亚阈值区具有明显反短沟效应的长度值.在此沟道长度的作用下,不同电压下具有相同驱动能力的NMOS和PMOS宽度比相比传统方法会发生变化.图 6为应用反短沟效应和反窄沟效应后,室温 (25 ℃) 下,宽度比随电压变化的趋势,与采用传统方法的图 2比较可知:正常电压下,采用本方法设计的宽度比会增大;然而,当电压降低到亚阈值后,晶体管的尺寸开销大大降低,在0.2 V和FNSP工艺角下,宽度比只为24左右,约为传统方法尺寸开销的25%.出现这种现象的原因在于,正常电压下晶体管没有反短沟效应和反窄沟效应,本文所选取的沟道长度值会造成PMOS和NMOS驱动能力的差距比传统方法更大,导致PMOS必须付出更大的面积开销去匹配NMOS;而在低电压下,反短沟效应和反窄沟效应的出现会有效地作用于晶体管,进而显著地降低宽度比.因此,在低电压下进行晶体管的尺寸设计时,反短沟效应和反窄沟效应的应用能大幅优化宽度比,提升性能.

|

图 6 应用RSCE和RNCE后宽度比变化 Figure 6 Rate trend with RSCE and RNCE |

将温度因素引入本文方法后,从全局观察,宽度比依旧呈现类似于传统方法的随电压和温度的降低而上升的趋势,但是上升速率明显放缓,如图 7所示.最恶劣的情况仍然出现在FNSP工艺角,电压为0.2 V的条件下,此时3个温度下的宽度比分别为51,24和15.相比图 3的传统方法,宽度比分别为传统方法的16.7%, 25.0%, 33.3%.因此, 本文方法相比传统方法在低电压下对面积的优化非常显著,特别是考虑温度因素后,在越低的温度下越有优化效果.

|

图 7 不同温度和工艺角下宽度比变化 Figure 7 Rate trend in different temperatures and corners |

本文基于新的尺寸调整方法进行了亚阈值SRAM单元的设计,用以验证该方法的有效性.根据NMOS和PMOS所具有的反短沟和反窄沟特性,对10管SRAM单元进行了如图 8所示的尺寸调整.

|

图 8 反短沟和反窄沟在单元中的应用 Figure 8 Employment of the RSCE and RNCE in the SRAM cell |

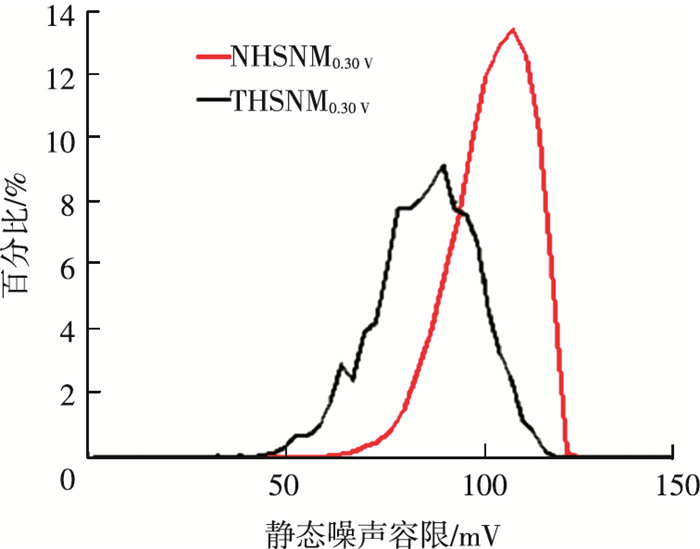

为提高亚阈值区的保持噪声容限,需要匹配背靠背反相器中PMOS和NMOS的驱动能力.由于PMOS的反短沟效应明显,所以加长PMOS的沟道长度,以增强其驱动能力.而NMOS的反窄沟效应明显,因此增大NMOS的宽度,以削弱其驱动能力,从而与PMOS的匹配度更高.在设计中PMOS采用2倍的最小沟道长度以获得1.45倍的驱动电流,NMOS采用较大的宽度 (W=300 nm) 以更加匹配PMOS.在0.3 V电压下,对传统SRAM单元和本文设计的SRAM单元做了10 000次的蒙特卡罗分析,如图 9所示. 图 9表明,传统SRAM单元 (黑色曲线) 平均的保持噪声容限是84.8 mV,方差16.5,而本文SRAM单元 (红色曲线),平均保持噪声容限是110.7 mV,方差11.8,两项指标分别提升30.5%和28.48%.

|

图 9 6管单元和本文单元的噪声容限比较 Figure 9 Static noise margin comparison |

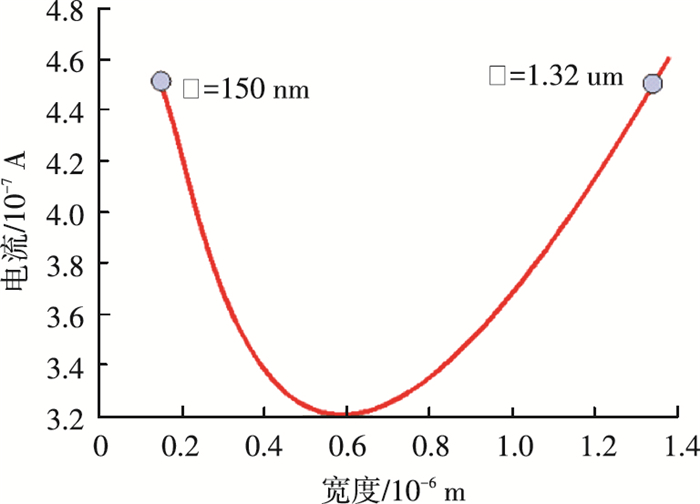

同时,存取晶体管M5和M6采用最小宽度以提高SRAM的写能力.在此宽度下,M5和M6因反窄沟效应产生的驱动能力相当于晶体管在1.32 um宽度下的驱动能力,如图 10所示.同理,读出路径M7,M8,M9也采用最小的宽度,用以加快读出速度,提高性能.因此,本文提出的尺寸调整方法,在付出较小面积和电路代价的同时,又能有效地提高低电压下的读写能力,提升SRAM整体性能.

|

图 10 不同宽度的NMOS的驱动能力 Figure 10 NMOS current comparison |

在相同噪声容限和读写能力的条件下,归一化比较0.3 V电压下传统方法和本文方法的面积消耗.本文的方法不局限于特定的工艺节点,所以利用传统和本文方法分别设计了130 nm和65 nm的SRAM单元.

在130 nm工艺下,把传统方法付出的单元面积总代价视为1,则使用本文提出的方法,尺寸为0.24,面积开销显著降低, 结果见表 1.在65 nm工艺下,把传统方法付出的单元面积总代价视为1,则使用本文提出的方法,尺寸为0.25,面积开销同样减小75%,所以此方法对面积的优化是通用的,不受工艺节点限制,结果见表 2.

| 表 1 130 nm工艺下传统方法和本文方法比较 Table 1 Area comparison between conventional way and proposed way at 130 nm |

| 表 2 65 nm工艺下传统方法和本文方法比较 Table 2 Area comparison between conventional way and proposed way at 65 nm |

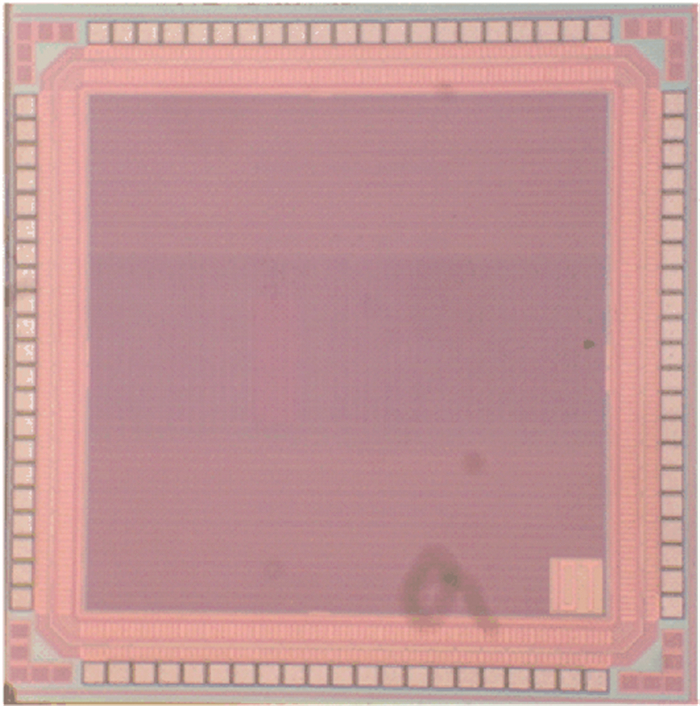

将本文的10管SRAM在中芯国际130 nm工艺下进行流片,裸片如图 11所示.所有的PAD都采用模拟PAD,以保证低电压信号的传输.

|

图 11 SRAM芯片裸片 Figure 11 SRAM die |

最终测试结果表明,写操作的最低电压为0.3 V,读操作的最低工作电压为0.32 V,此时的工作频率为800 kHz,功能如图 12所示.本文与同类型的低电压SRAM进行了较为全面的比较,结果见表 3.由于本文的SRAM有更充分的噪声容限和读写能力,所以具有更优的降压空间,相比于参照的SRAM可以达到更低的操作电压,而且在性能和能耗上也具有优势.

|

图 12 亚阈值SRAM芯片功能 Figure 12 Function of subthreshold SRAM |

| 表 3 与同类型芯片比较结果 Table 3 Comparison with other SRAMs |

1) 研究了传统尺寸调整方法在亚阈值区的局限性,分析了其在低电压下引入的额外面积和电路开销问题.

2) 通过对反短沟效应和反窄沟效应的研究,将其引入到低电压的尺寸设计方法中,在保证性能的同时,有效节省面积开销,降低电路复杂度.

3) 基于新的尺寸设计方法,设计了亚阈值SRAM单元,改善了其在低电压下的噪声容限和读写能力.测试结果表明,SRAM能在0.32 V的低压下以800 kHz的频率稳定工作,其中读操作的最低电压为0.32 V,而写操作的最低电压为0.3 V,此时噪声容限提升30.5%.

| [1] | KHAYATZADEH M, LIAN Yong. Average 8-T differential sensing subthreshold SRAM with bit interleaving and 1k bits per bitline[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22(5): 971-982. DOI: 10.1109/TVLSI.2013.2265265 |

| [2] | KIMT H, LIU J, KIM C H. A voltage scalable 0.26 V, 64 k8-T SRAM with Vmin lowering techniques and deep sleep mode[J]. IEEE Journal of Solide-State Circuit, 2009, 44(6): 1785-1795. DOI: 10.1109/JSSC.2009.2020201 |

| [3] | KIM T H, KEANE J, EOM H, et al. Utilizingreverse short-channel effect for optimal subthreshold circuit design[J]. IEEE Transactions on Very Large Scale Integration Systems, 2007, 15(7): 821-829. DOI: 10.1109/TVLSI.2007.899239 |

| [4] | CALHOUN B H, CHANDRAKASAN A P. A 256-kb 65-nm Sub-threshold SRAM design for ultra-low-voltage operation[J]. IEEE Journal of Solide-State Circuit, 2007, 42(3): 680-688. DOI: 10.1109/JSSC.2006.891726 |

| [5] | VERMA N, CHANDRAKASAN A P. A 256 kb 65 nm 8-T Subthreshold SRAM employing sense amplifier redundancy[J]. IEEE Journal of Solide-State Circuit, 2008, 43(1): 141-149. DOI: 10.1109/JSSC.2007.908005 |

| [6] | TU M H, LIN J Y, TSAI M C, et al. Asingle-ended disturb-free 9-T subthreshold SRAM with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing[J]. IEEE Journal of Solide-State Circuit, 2012, 47(6): 1469-1482. DOI: 10.1109/JSSC.2012.2187474 |

| [7] | KULKARNI J P, KIM K, ROY K. A 160 mV robust Schmitt trigger based subthreshold SRAM[J]. IEEE Journal of Solide-State Circuit, 2007, 42(10): 2303-2313. DOI: 10.1109/JSSC.2007.897148 |

| [8] | KIM T H, LIU J, KEANE J, et al. A 0.2 V, 480 kb subthreshold SRAM with 1k cells per bitline forultra-low-voltagecomputing[J]. IEEE Journal of Solid-State Circuits, 2008, 43(2): 518-529. DOI: 10.1109/JSSC.2007.914328 |

| [9] | LO C H, HUANG S Y. P-P-N Based 10-T SRAM cell for low-leakage and resilient subthreshold operation[J]. IEEE Journal of Solid-State Circuits, 2011, 46(3): 695-704. DOI: 10.1109/JSSC.2010.2102571 |

| [10] | ZHAI Bo, HANSON S, BLAAUW D, et al. A variation-tolerant sub-200 mV 6-T subthreshold SRAM[J]. IEEE Journal of Solid-State Circuits, 2008, 43(10): 2338-2348. DOI: 10.1109/JSSC.2008.2001903 |

| [11] |

张苏敏, 陈黎明, 袁甲, 等. 面向亚阈值的脉冲生成电路设计[J].

微电子学与计算机, 2014, 31(9): 118-125.

ZHANG Sumin, CHEN Liming, YUAN Jia, et al. Design of subthreshold pulse generator[J]. Microelectronics & Computer, 2014, 31(9): 118-125. |

| [12] | LU C Y, SONG J M. Reverse short-channel effects on threshold voltage insubmicrometer salicide devices[J]. IEEE Electron Device Letters, 1989, 10(10): 446-448. DOI: 10.1109/55.43095 |

| [13] |

刘鸣, 陈虹, 贾晨, 等. 亚阈值32位数据通路设计[J].

清华大学学报 (自然科学版), 2010, 50(1): 9-12.

LIU Ming, CHEN Hong, JIA Chen, et al. Design of a sub-threshold 32-bit data bath[J]. Journal of Tsinghua.University (Science & Technology), 2010, 50(1): 9-12. |

2017, Vol. 49

2017, Vol. 49