物联网系统对低功耗有着极高的需求,随着物联网技术的兴起和CMOS工艺技术的进步,降低电路系统的功耗成为了当前主要的研究方向[1-3]。运算放大器作为模拟电路和数模混合电路中的基础模块,其性能直接决定了整个电路系统的性能[4]。因此功耗的降低不能以牺牲运算放大器的性能为代价,如何在低功耗电路的设计中保持运算放大器的高性能成为了当前研究的难点。

AB类放大器的动态电流可以不受其静态电流的限制[5],因此可以在实现低功耗前提下实现高的动态电流,从而实现高性能[6-11]。AB类放大器的这一特性使其在低功耗应用中受到了较大的关注,目前已经提出了多种AB类放大器技术。

折叠共源共栅AB类放大器可以实现很高的直流增益和增益带宽积(gain-bandwidth product, GBW)[12-15],但是共源共栅晶体管的存在,限制了输出范围和转换速率(slew rate, SR)的提升。一种叫做超级AB类运算放大器的电路备受关注[5, 16-17],其输出级的动态电流与输入电压的4次方成正比,因此可以实现很高的转换速率,同时输出级没有用到共源共栅晶体管,因此可以实现较高的输出范围,但是其电路的等效跨导较低,因此限制了直流增益和增益带宽积的提高。综上,目前已有的AB类放大器很难同时实现较高的大信号性能和小信号性能。

本文提出了一种改进型的超级AB类运算放大器,提出了基于差分对的电流复用技术,该技术将输入晶体管产生的偏置电流再次利用,提高了电路的输出电流,从而解决了传统的超级AB类放大器增益带宽积和直流增益较低的问题。输入晶体管的偏置电流使用了自适应偏置电路,其偏置电流随差模电压的增大而增大,实现了低的静态电流和高的动态电流,因此放大器工作在AB类。局部共模反馈技术的使用同样提高了动态电流。整体电路将上述3种技术结合,提高了运算放大器的转换速率、增益带宽积和直流增益。

1 电路结构及关键电路分析本文提出的电路结构框图如图 1所示,与传统的运算放大器相比,本文用自适应的偏置电流源取代了输入差动对中传统的固定尾电流源。晶体管M2A、M2B、M3A和M3B尺寸相同,因此实现了电流的复制。同时电流复用电路和局部共模反馈电路进一步提高了转换速率、增益带宽积和直流增益。电路在不需要额外补偿电路的前提下便可以实现足够的相位裕度。接下来对关键的电路模块进行分析。

|

图 1 电路结构框图 Fig. 1 Block diagram of circuit architecture |

本文设计的自适应偏置电路在输入电压只有共模电压时提供很低的偏置电流,而存在差模输入电压时,其偏置电流可以随差模电压的提高而迅速增加。

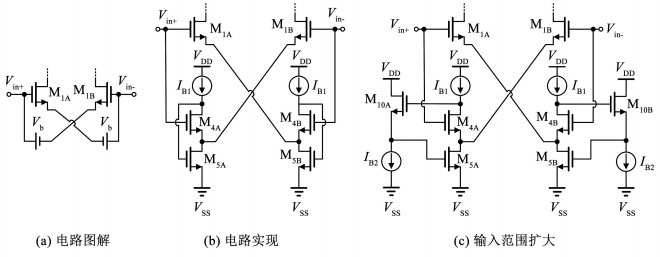

两个交叉耦合的电平移位器可以实现上述功能[5, 16],如图 2(a)所示。当输入差模电压为零时,晶体管M1A和M1B的栅源电压等于Vb,因此具有相同的静态电流。如图 2(b)所示的翻转电压跟随器(flipped voltage follower, FVF)可以实现电平移位的功能[18],其中M1A、M1B、M4A和M4B具有相同的尺寸,静态时这4个晶体管具有相同的栅源电压,因此M1A和M1B的静态电流为IB1。

|

图 2 自适应偏置电路的实现 Fig. 2 Realization of adaptive bias circuit |

当输入一个差模电压Vid,则Vin+提高Vid/2,Vin-降低Vid/2,同时由于M4A和M4B的电平移位,M1B的源极提高Vid/2,M1A的源极降低Vid/2,因此M1A的栅源电压VGS提高Vid,M1B的栅源电压下降Vid。Vid越大,则输入晶体管M1A和M1B的VGS变化越大,偏置电流变化越大。

当输入的差模电压为小信号vid时,M1A和M1B产生的小信号电流分别为i1A=gm1vid和i1B=-gm1vid,其中gm1表示晶体管M1A和M1B的跨导。小信号差模电流id为

| $ i_{\mathrm{d}}=i_{1 \mathrm{~A}}-i_{1 \mathrm{~B}}=2 g_{\mathrm{m} 1} v_{\mathrm{id}} $ | (1) |

式(1)表明差分对的等效跨导为2gm1,与传统的固定尾电流偏置的差分对相比,跨导提高了1倍。当输入大信号电压Vid时,晶体管M1A和M1B的漏电流分别为

| $ I_{1 \mathrm{~A}}=\frac{1}{2} \beta_1\left(V_{\mathrm{GSQ}}-V_{\mathrm{TH}}+V_{\mathrm{id}}\right)^2=\frac{1}{2} \beta_1\left(\sqrt{\frac{2 I_{\mathrm{B} 1}}{\beta_1}}+V_{\mathrm{id}}\right)^2 $ | (2) |

| $ I_{1 \mathrm{~B}}=\frac{1}{2} \beta_1\left(V_{\mathrm{GSQ}}-V_{\mathrm{TH}}-V_{\mathrm{id}}\right)^2=\frac{1}{2} \beta_1\left(\sqrt{\frac{2 I_{\mathrm{B} 1}}{\beta_1}}-V_{\mathrm{id}}\right)^2 $ | (3) |

式中:VGSQ为静态时的栅源电压,VTH为晶体管的阈值电压,β=μnCOX(W/L)为晶体管的跨导系数,μn为载流子迁移率,COX为栅氧化层的单位面积电容,W和L分别为晶体管的宽度和长度,IB1为静态电流。

从式(2)和式(3)可以看出,电流I1A和I1B不受静态偏置电流IB1的限制。如果Vid是一个比较小的值,M1A和M1B依然工作在饱和区,则差分对的差模电流为

| $ I_{\mathrm{d}}=I_{1 \mathrm{~A}}-I_{1 \mathrm{~B}}=\sqrt{8 I_{\mathrm{B} 1} \beta_1} V_{\mathrm{id}} $ | (4) |

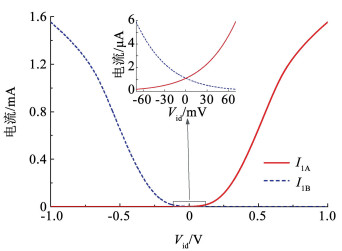

此时差模电流Id与差模电压Vid成线性关系。但是如果Vid是一个比较大的正向电压,则I1A将会急剧增大,I1B将会急剧减小,甚至接近0,M1B进入截止区,以至于I1A远远大于I1B,计算差模电流时可以忽略I1B的值,差模电流Id≈I1A,此时差模电流与差模电压的平方成正比。同理,如果Vid是一个比较大的反向电压,则可以忽略I1A的值,差模电流Id≈I1B。综上所述,如果Vid比较小,则差模电流与差模电压成线性关系;如果Vid比较大,则差模电流与差模电压的平方成正比。I1A和I1B随Vid变化的仿真结果如图 3所示,当Vid较小时,I1A和I1B随Vid线性增加,当Vid较大时,I1A和I1B随Vid的增加急剧增加,因此图 3的仿真结果验证了本节的理论分析。

|

图 3 I1A和I1B随输入电压变化的仿真结果 Fig. 3 Simulation results of I1A and I1B with input voltage |

FVF的缺点是输入电压的范围有限,如图 2(b)所示,如果输入电压Vin增大,则晶体管M4A和M4B的源极电压会同时增大,导致其源漏电压VDS4减小,如果Vin的值太大,会导致M4A和M4B进入线性区。为使晶体管都工作在饱和区,具体的输入电压范围为

| $ V_{\mathrm{GS4A}}+V_{\mathrm{DSSA}, \mathrm{sat}}<V_{\mathrm{in}}<V_{\mathrm{GS5A}}+V_{\mathrm{GS4A}}-V_{\mathrm{DS4A}, \mathrm{sat}} $ | (5) |

式中VGsi和VDSi, sat分别为对应的晶体管的栅源电压和过驱动电压。因此Vin的大小为

| $ V_{\text {inpp }}=V_{\mathrm{GS} 5 \mathrm{~A}}-V_{\mathrm{DS} 4 \mathrm{~A}, \text { sat }}-V_{\mathrm{DS} 5 \mathrm{~A} \text {, sat }} $ | (6) |

为了扩大Vin的范围,可以在M4A的漏极和M5A栅极之间添加一个电平移位器,如图 2(c)所示,M10A、M10B和电流源IB2构成的源跟随器便可以实现电平移位的功能。Vin的范围提高了VGS10A,因此输入变为

| $ V_{\text {inpp }}=V_{\mathrm{GS} 10 \mathrm{~A}}+V_{\mathrm{GS} 5 \mathrm{~A}}-V_{\mathrm{DS} 4 \mathrm{~A}, \text { sat }}-V_{\mathrm{DS} 5 \mathrm{~A} \text {, sat }} $ | (7) |

为了实现较大的VGS10A,M10A可以通过选择非常小的宽长比来扩大输入范围。

1.2 电流复用电路在本文提出的电路中,输入差分对产生的差模电流在到达输出级之前,会由电流复用电路进行提高。

电流复用电路的图解如图 4(a)所示,由1.1节可知I1A和I1B分别是M1A和M1B产生的电流。以左边电路为例,电流复用电路以α的倍数复制电流I1B,之后对电流I1A进行分流产生新的电流Ip=I1A-αI1B。右边电路同理, In=I1B-αI1A。电路的实现方法如图 4(b)所示,晶体管M6A和M6B会以λ的倍数复制M5A和M5B的电流。由于M1B的电流流经M5A,所以M6A的电流可以反映M1B电流的变化。同理,M6B的电流可以反映M1A电流的变化。

|

图 4 电流复用电路 Fig. 4 Current reuse circuit |

考虑一个小信号差分输入电压,M1B产生的小信号电流i1B会流经M5A,因此M5A的小信号电流i5A等于i1B。同理,M5B的小信号电流i5B等于i1A。此时α=λ,因此产生的小信号差模电流idn为

| $ i_{\mathrm{dn}}=i_{\mathrm{p}}-i_{\mathrm{n}}=(1+\alpha)\left(i_{1 \mathrm{~A}}-i_{1 \mathrm{~B}}\right)=(1+\alpha) i_{\mathrm{d}} $ | (8) |

由式(8)可知,所提出的电流复用电路产生的小信号差模电流是传统差分输入对的1+α倍。因此电流复用电路可以提高小信号差模电流,从而提高电路的跨导。

对于大信号,当输入一个比较大的正向差分输入电压时,I1A会急剧增大,其值远远大于静态电流IB1,同时I1B会急剧减小,甚至接近0。此时流经M6A的电流值约为λIB1,远远小于I1A,因此Ip≈I1A。而I1B接近0,因此M6B将会进入线性区,In≈0,差模电流约等于I1A。同理,对于一个比较大的反向差分输入电压,差模电流约等于I1B。

在同样的功耗和负载电容的情况下,有无电流复用电路的增益频率响应的前仿真对比结果如图 5所示,由图 5可知,没有电流复用电路的时候,增益带宽积为1.65 MHz;有电流复用电路的时候,增益带宽积为2.53 MHz。图 5表明电流复用电路可以显著提高增益带宽积和直流增益,验证了本节的分析。

|

图 5 增益频率响应的仿真 Fig. 5 Simulation of gain frequency response |

1.3局部共模反馈电路

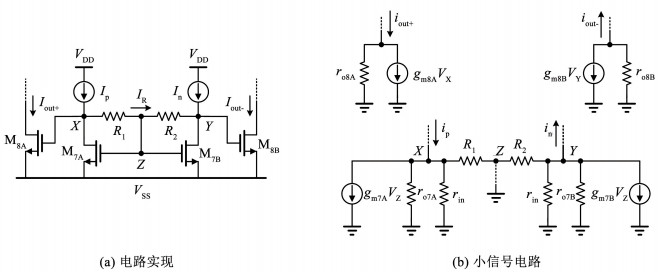

局部共模反馈电路对电流复用电路输出的差模电流进一步处理,再次增大差模电流,最终到达输出级,再次提高电路的大信号和小信号性能[19]。局部共模反馈电路如图 6(a)所示,M7A和M7B的栅极连接到共同的节点Z,然后通过电阻R1和R2连接到各自的漏极,其中R1=R2=R。

|

图 6 局部共模反馈电路 Fig. 6 Local common mode feedback circuit |

静态情况下Ip=In=(1-2λ)IB1,没有电流流过电阻R1和R2,因此VX=VY=VZ,M7A和M7B可以看成是二极管连接。考虑小信号差分输入电流ip和in,图 6(b)显示了局部共模反馈电路的小信号模型,其中gmi和roi分别表示相应晶体管Mi的跨导和输出电阻,rin表示输入电流源的电阻。节点Z两侧的电路完全对称,因此节点Z可以作为小信号地,即VZ=0。节点X和节点Y处的小信号电阻为

| $ R_X=R_Y=R_{X, Y}=R\left\|r_{\mathrm{o} 7}\right\| r_{\mathrm{in}} $ | (9) |

其中ro7=ro7A=ro7B。iout+和iout-的表达式分别为gm8RX, Yip和gm8RX, Yin,并且gm8=gm8A=gm8B。因此局部共模反馈电路的电流增益为gm8RX, Y,可以通过提高R1和R2的阻值R来提升增益。

对于一个大信号输入电流,忽略沟道长度调制效应,由于M7A和M7B的栅级相连,因此M7A和M7B的漏电流为共模电流Icm=(Ip+In)/2,流经R1和R2的电流IR=Idn/2=(Ip-In)/2为差模电流。此时X、Y和Z点的节点电压为

| $ \left\{\begin{array}{l} V_Z=V_{\mathrm{TH}}+\sqrt{\frac{2 I_{\mathrm{cm}}}{\beta_7}} \\ V_X=V_Z+I_{\mathrm{R}} R_1 \\ V_Y=V_Z-I_{\mathrm{R}} R_2 \end{array}\right. $ | (10) |

如果输入为正向的大信号电流,即Ip>In,则VX会有一个比较大的正向增大,流经M8A的电流Iout+变大为

| $ I_{\text {out }+}=\frac{\beta_8}{2}\left(V_X-V_{\mathrm{TH}}\right)^2=\frac{\beta_8}{2}\left(\sqrt{\frac{2 I_{\mathrm{cm}}}{\beta_7}}+I_{\mathrm{R}} R\right)^2 $ | (11) |

其中β8为M8A和M8B的跨导系数。VY会有一个比较大的降低,导致流经M8B的电流Iout-比静态时大大减小,导致M8B进入截止区。此时Iout=Iout+-Iout-≈Iout+。同理,如果输入为反向的大信号电流,即Ip<In,则VY会有一个比较大的正向增大,流经M8B的电流Iout-变大为

| $ I_{\text {out }-}=\frac{\beta_8}{2}\left(V_Y-V_{\mathrm{TH}}\right)^2=\frac{\beta_8}{2}\left(\sqrt{\frac{2 I_{\mathrm{cm}}}{\beta_7}}-I_{\mathrm{R}} R\right)^2 $ | (12) |

VX会有一个比较大的降低,导致流经M8A的电流Iout+大大减小。此时Iout=Iout+-Iout-≈-Iout-。在式(11)中IR>0,在式(12)中-IR>0。因此可以将式(11)、(12)结合成Iout的通用公式:

| $ I_{\text {out }}=I_{\text {out }+}-I_{\text {out }-} \approx \pm \frac{\beta_8}{2}\left(\sqrt{\frac{2 I_{\mathrm{cm}}}{\beta_7}}+\left|I_{\mathrm{R}}\right| R\right)^2 $ | (13) |

当Ip>In,则Iout>0;当Ip<In,则Iout<0。由式(13)可以看出,局部共模反馈电路对输入电流进行了平方关系的提升,极大地提高了大信号性能。

2 整体电路分析电路的完整结构如图 7所示,下面对电路的小信号性能和大信号性能进行分析。

|

图 7 提出的AB类运算放大器 Fig. 7 Proposed class AB operational amplifier |

当在输入端输入一个小信号电压vid时,在输出端会产生小信号输出电流iout,结合上一节对3个电路模块的分析,可以得到输出的小信号电流为

| $ i_{\text {out }}=i_{\text {out }+}-i_{\text {out }-}=2(1+\alpha) g_{\mathrm{m} 1} g_{\mathrm{m} 8} R_{X, Y} v_{\mathrm{id}} $ | (14) |

因此电路的整体跨导为

| $ G_{\mathrm{m}}=\frac{i_{\text {out }}}{v_{\text {id }}}=2(1+\alpha) g_{\mathrm{m} 1} g_{\mathrm{m} 8} R_{X, Y} $ | (15) |

并且电路的增益带宽积GBW=Gm/(2πCL), 直流增益Av=GmRout。由式(9)、(15)可知,可以通过提高电阻值R来提高电路的小信号性能。但是随着R的增大,节点X和Y的寄生极点会降低,如果其寄生极点小于GBW,则会造成系统的不稳定。节点X和Y形成的极点为次主极点fnd, 有

| $ f_{\mathrm{nd}}=\frac{1}{2 {\rm{\mathsf{π}}} R_{X, Y} C_{X, Y}} $ | (16) |

电路的相位裕度(phase margin, PM)由下式给出:

| $ \begin{gathered} \mathrm{PM} \approx 90^{\circ}-\arctan \left(\frac{\mathrm{GBW}}{f_{\mathrm{nd}}}\right) \approx \\ 90^{\circ}-\arctan \left(\frac{2(1+\alpha) g_{\mathrm{m} 1} g_{\mathrm{m} 8}\left(R_{X, Y}\right)^2 C_{X, Y}}{C_{\mathrm{L}}}\right) \end{gathered} $ | (17) |

其中CX, Y≈CGS8+CGB8为节点X和Y的寄生电容。

式(17)为考虑了输出主极点和次主极点的近似表达式,其他的极点由于分布在高频,对电路的稳定性影响很小。在给定的负载电容和要求的相位裕度的情况下,式(17)可以帮助估算最大的RX, Y。为了保证系统的稳定性,R1和R2的阻值R要远远小于晶体管的输出电阻ro,局部共模反馈电路的输入电阻rin=ro3‖ro6,其中ro3=ro3A=ro3B,ro6=ro6A=ro6B,因此由式(9)可得出RX, Y≈R。

2.2 大信号分析图 7中红色的箭头表示了输入电压产生的电流传输路径,最终会在输出端产生输出电流Iout。Iout的表达式由式(13)给出,其中Icm和IR由Ip和In决定。根据1.2节的分析,当输入电压产生大的差分电流的时候,电流复用电路分流I1A和I1B的影响会大大降低。因此Ip≈I1A,In≈I1B。对于一个大的正向的Vid,观察式(2)括号中的两项,

综上,根据式(13),可以得到输出电流Iout, 从而得到转换速率SR的表达式:

| $ \mathrm{SR}=\frac{I_{\text {out }}}{C_{\mathrm{L}}} \approx \pm \frac{\beta_8}{2 C_{\mathrm{L}}}\left(\sqrt{\frac{\beta_1 V_{\mathrm{id}}^2}{2 \beta_7}}+\frac{\beta_1 R}{4} V_{\mathrm{id}}^2\right)^2 $ | (18) |

通过式(18)可以发现,SR与Vid的4次方成正比,这是由于自适应偏置电路和局部共模反馈电路的输出都会对输入进行平方关系的提升。所以随着Vid的增加,Iout会迅速增加。SR还与晶体管的跨导系数β有关,可以通过提高晶体管的宽长比来提升SR,但是宽长比的增加会增加节点的寄生电容,因此在设计电路参数的时候应该折中考虑,在满足稳定性的前提下,尽量增大SR。

3 版图设计和仿真结果在运算放大器的版图设计中,对称的晶体管和电阻需要在版图上进行匹配,本文提出的电路进行了共质心交叉匹配的布局方式并在外围添加了dummy晶体管,同时金属走线也尽量做到了对称,使得版图对称节点的寄生效应尽量一致。

基于180 nm CMOS工艺进行电路以及版图设计,电路的整体版图如图 8所示,包括焊盘的芯片总面积为390 μm×320 μm,核心面积为200 μm×120 μm,其中电阻占据了主要的面积。表 1总结了晶体管的尺寸,为了获得高的输入范围,M10A和M10B选择了很小的宽长比。电阻R1和R2利用高阻多晶硅层进行制造,阻值为280 kΩ。电源电压VDD为2 V,偏置电流IB1和IB2分别为1 μA和0.25 μA。

|

图 8 AB类运算放大器整体版图 Fig. 8 Layout of proposed class-AB operational amplifier |

| 表 1 晶体管参数 Tab. 1 Transistor parameters |

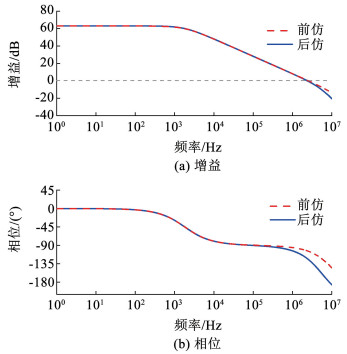

对版图进行寄生参数提取后,在负载电容CL为70 pF的情况下对电路进行后仿真,总静态电流为11.5 μA。放大器的开环频率响应如图 9和图 10所示,其中图 9为前仿真和后仿真的性能对比,前后仿的单位增益带宽积分别2.53、2.38 MHz。可以发现频率在单位增益带宽积以下时,前后仿的曲线基本重合,频率大于单位增益带宽积时,由于版图的寄生效应,电路引入了额外地寄生极点,因此后仿真的增益和相位相对前仿真都要下降得更快。图 10为不同工艺角下的性能对比,在TT、FF和SS三种工艺角下,单位增益带宽积分别为2.38、2.83、1.96 MHz,直流增益分别为为63、61、64 dB,相位裕度分别为57°、55°、61°。

|

图 9 前后仿真下的开环频率响应 Fig. 9 Open-loop frequency responses in pre-simulation and post-simulation |

|

图 10 不同工艺角的开环频率响应 Fig. 10 Open-loop frequency responses of different corners |

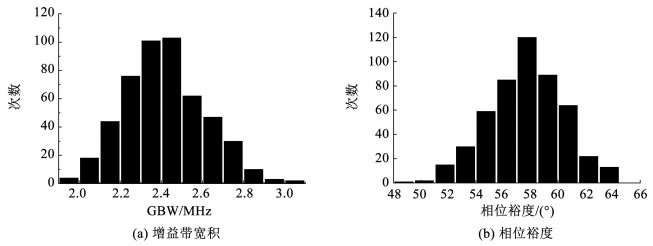

考虑随机的工艺偏差和器件之间的失配,对电路进行了小信号的蒙特卡洛仿真,采样500次,仿真结果如图 11所示,电路的单位增益带宽积和相位裕度的平均值分别为2.42 MHz和57.66°,标准差分别为0.2 MHz和2.71°,其值与TT工艺角下较为接近。仿真结果表明,满足相位裕度的情况下,该电路实现了较高的单位增益带宽积和直流增益。

|

图 11 小信号的蒙特卡洛仿真结果 Fig. 11 Monte Carlo simulation results of small signal |

将运算放大器接成单位增益缓冲器来进行大信号特性仿真,图 12显示了电路的大信号瞬态响应,其中图 12(a)为前仿真和后仿真的性能对比,输入电压在0.5~1.5 V之间变化,并且变化时间为1 ns。前仿真和后仿真的输出电压正向转换速率分别为24.1、23.55 V/μs,反向转换速率分别为-43.95、-31.47 V/μs。图 12(b)、12(c)和12(d)分别表示TT、FF和SS三种工艺角下的大信号瞬态响应。在TT、FF和SS三种工艺角下,输出电压的正向转换速率分别为23.55、25.61、21.59 V/μs,反向转换速率分别为-31.47、-28.61、-34.29 V/μs。对电路进行大信号蒙特卡洛仿真,采样500次,仿真结果如图 13所示,电路正负转换速率的平均值分别为23.51、-31.52 V/μs,标准差分别为0.85、0.7 V/μs。仿真结果表明,该电路在功耗较低的情况下获得了较高的转换速率。

|

图 12 大信号瞬态响应 Fig. 12 Large-signal transient response |

|

图 13 大信号的蒙特卡洛仿真结果 Fig. 13 Monte Carlo simulation results of large signal |

表 2总结了本文提出的电路与当前其它已知的AB类放大器在相同工艺节点下的主要性能总结和对比。其中VDD为电源电压,CL为负载电容,SR+为正向转换速率,SR-为负向转换速率,GBW为增益带宽积。为了定量地比较各个文献中电路的性能,可以使用下面的品质因数进行比较:

| 表 2 AB类运算放大器主要性能对比 Tab. 2 Main performance comparison of class AB operational amplifiers |

| $ \mathrm{FOM}_{\mathrm{L}}=\mathrm{SR} \frac{C_{\mathrm{L}}}{P} $ | (19) |

| $ \mathrm{FOM}_{\mathrm{S}}=\mathrm{GBW} \frac{C_{\mathrm{L}}}{P} $ | (20) |

其中P表示电路的静态功耗,式(19)反映了电路的大信号性能,式(20)反映了电路的小信号性能。可以发现,本文具有最高的FOMS值和最高的FOML值。根据式(18),转换速率与静态功耗无关,因此在一定GBW的要求下,可以进一步降低静态功耗来获得更高的FOML值。

4 结论1) 提出了电流复用电路,并将其与自适应偏置电路和局部共模反馈电路相结合,将差分输入电压产生的差分电流不断放大,最终到达输出端,提高了电路的输出电流,从而提高了转换速率、增益带宽积和直流增益。

2) 基于180 nm CMOS工艺,对电路进行设计和验证,仿真结果表明所提出的AB类运算放大器在低功耗的前提下获得了较好的大信号和小信号性能,在低功耗领域具有较高的应用价值。同时,所提出的AB类放大器与近几年提出的AB类放大器相比也具有一定的优势,其转换速率和增益带宽积的品质因数都获得了更高的数值。

3) 基于差分对管的电流复用技术提出了一种具体的电路实现方式,即复制FVF电路的电流,而FVF电路反映了输入晶体管电流的变化,因此实现了对差分电流的复用。

| [1] |

WANG Keping, OTIS B, WANG Zhigong. A 580μW 2.4 GHz ZigBee receiver front end with transformer coupling technique[J]. IEEE Microwave and Wireless Components Letters, 2018, 28(2): 174. DOI:10.1109/LMWC.2017.2787064 |

| [2] |

WANG Keping, QIU Lei, KOO J, et al. Design of 1.8-mW PLL-Free 2.4 GHz receiver utilizing temperature-compensated FBAR resonator[J]. IEEE Journal of Solid-State Circuits, 2018, 53(6): 1628. DOI:10.1109/JSSC.2018.2801829 |

| [3] |

TOLEDO P, CROVETTI P, AIELLO O, et al. Design of digital OTAs with operation down to 0.3 V and nW power for direct harvesting[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2021, 68(9): 3693. DOI:10.1109/TCSI.2021.3089339 |

| [4] |

张为, 彭彦豪, 齐步坤, 等. 前馈型轨到轨恒跨导恒增益CMOS运算放大器[J]. 华中科技大学学报(自然科学版), 2011, 39(1): 19. ZHANG Wei, PENG Yanhao, QI Bukun, et al. Feedforward rail to rail constant-gm constant gain CMOS operational amplifiers[J]. Journal of Huazhong University of Science and Technology(Natural Science Edition), 2011, 39(1): 19. DOI:10.13245/j.hust.2011.01.015 |

| [5] |

BELOSO-LEGARRA J, CRUZ-BLAS C A D L, LOPEZ-MARTIN A J, et al. Gain-boosted super class AB OTAs based on nested local feedback[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2021, 68(9): 3562. DOI:10.1109/TCSI.2021.3090154 |

| [6] |

雷鑑铭, 胡北稳, 桂涵姝, 等. 采用新型低成本共模反馈电路的全差分运放设计[J]. 浙江大学学报(工学版), 2013, 47(10): 1777. LEI Jianming, HU Beiwen, GUI Hanshu, et al. Design of fully differential operational amplifier with low cost common feedback circuit[J]. Journal of Zhejiang University(Engineering Science), 2013, 47(10): 1777. DOI:10.3785/j.issn.1008-973X.2013.10.012 |

| [7] |

BERNAL M R V, CELMA S, MEDRANO N, et al. An ultralow-power low-voltage class-AB fully differential OpAmp for long-life autonomous portable equipment[J]. IEEE Transactions on Circuits and Systems Ⅱ: Express Briefs, 2012, 59(10): 643. DOI:10.1109/TCSII.2012.2213361 |

| [8] |

SUTULA S, DEI M, TERES L, et al. Variable-mirror amplifier: a new family of process-independent class-AB single-stage OTAs for low-power SC circuits[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2016, 63(8): 1101. DOI:10.1109/TCSI.2016.2577838 |

| [9] |

NADERI M H, PRAKASH S, SILVA-MARTINEZ J. Operational transconductance amplifier with class-B slew-rate boosting for fast high-performance switched-capacitor circuits[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2018, 65(11): 3769. DOI:10.1109/TCSI.2018.2852273 |

| [10] |

POURASHRAF S, RAMIREZ-ANGULO J, LOPEZ-MARTIN A J, et al. A highly efficient composite class-AB-AB miller Op-Amp with high gain and stable from 15 pF up to very large capacitive loads[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018, 26(10): 2061. DOI:10.1109/TVLSI.2018.2830365 |

| [11] |

AKBARI M, HASHEMIPOUR O, MORADI F. A high slew rate CMOS OTA with dynamic current boosting paths[C]//2018 IEEE International Symposium on Circuits and Systems. Florence, Italy: IEEE, 2018: 1. DOI: 10.1109/ISCAS.2018.8350926

|

| [12] |

WANG Yongqing, ZHANG Qisheng, YU S S, et al. A robust local positive feedback based performance enhancement strategy for non-recycling folded cascode OTA[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2020, 67(9): 2897. DOI:10.1109/TCSI.2020.2988310 |

| [13] |

GARDE M P, LOPEZ-MARTIN A, CARVAJAL R G, et al. Super class-AB recycling folded cascode OTA[J]. IEEE Journal of Solid-State Circuits, 2018, 53(9): 2614. DOI:10.1109/JSSC.2018.2844371 |

| [14] |

LOPEZ-MARTIN A J, GARDE M P, ALGUETA J M, et al. Enhanced single-stage folded cascode OTA suitable for large capacitive loads[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2018, 65(4): 441. DOI:10.1109/TCSII.2017.2700060 |

| [15] |

ASSAD R S, SILVA-MARTINEZ J. The recycling folded cascode: a general enhancement of the folded cascode amplifier[J]. IEEE Journal of Solid-State Circuits, 2009, 44(9): 2535. DOI:10.1109/JSSC.2009.2024819 |

| [16] |

LOPEZ-MARTIN A J, BASWA S, RAMIREZ-ANGULO J, et al. Low-voltage super class AB CMOS OTA cells with very high slew rate and power efficiency[J]. IEEE Journal of Solid-State Circuits, 2005, 40(5): 1068. DOI:10.1109/JSSC.2005.845977 |

| [17] |

GALAN J A, LOPEZ-MARTIN A J, CARVAJAL R G, et al. Super class-AB OTAs with adaptive biasing and dynamic output current scaling[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2007, 54(3): 449. DOI:10.1109/TCSI.2006.887639 |

| [18] |

CARVAJAL R G, RAMIREZ-ANGULO J, LOPEZ-MARTIN A J, et al. The flipped voltage follower: a useful cell for low-voltage low-power circuit design[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2005, 52(7): 1276. DOI:10.1109/TCSI.2005.851387 |

| [19] |

RAMIREZ-ANGULO R, HOLMES M. Simple technique using local CMFB to enhance slew rate and bandwidth of one-stage CMOS op-amps[J]. Electronics Letters, 2002, 38(23): 1409. DOI:10.1049/el:20020764 |

2023, Vol. 55

2023, Vol. 55