2. 抗辐射集成电路国防科技重点实验室(西安微电子技术研究所), 西安 710065

2. National Key Laboratory of Science and Technology on Radiation-Hardened Integrated Circuits (Xi'an Microelectronics Technology Institute), Xi'an 710065, China

随着集成电路特征尺寸的减小,微电子器件的阈值电荷和工作电压不断降低,使得空间应用的大规模集成电路中软错误率不断增加[1-3]。软错误主要是由SET电压在逻辑链路的终端被锁存或被存储单元捕获形成的。面对日益突出的软错误增加趋势,电路设计者从器件结构到系统层面使用了不同的辐射加固手段。目前,国内外较为成熟的辐射加固电路主要以65 nm工艺节点为主,形成了完备的辐射加固IP核和电路产品。在所有的辐射加固方法中,越靠近底层,加固的方法往往越能被广泛应用。从加固效果与成本之间折中考虑,电路设计加固的重点在于器件版图层面。在版图设计中,65 nm节点的主要加固方法有增加体阱接触、保护环技术、保护漏技术和利用脉冲窄化效应等[4-6]。然而,在越来越先进的工艺制程中,大部分的现有方法已经不能与设计规则很好地兼容,因此产生了新的设计挑战。

在数字集成电路设计中,与非门作为标准单元中常用的基本模块,是数字逻辑电路的重要支撑。在目前公开报道的加固方法中[7-8],该逻辑门作为通用的单元,与其他基本逻辑门一起被统一加固。文献[9]提出了一种冗余的设计方法,通过增加3个额外的晶体管形成了双端输入、双端输出的结构,在一定程度上缓解了输出节点的单粒子瞬态。但是该方法使得单个门的面积增加了近乎一倍。文献[10]指出,利用逻辑掩蔽的方法,能在其中一个输入端固定接“0”的状态下,不管另外一端的输入是否变化,都能起到对SET免疫的效果,但是该方法完全依赖于输入,对于输入动态变化的数字逻辑加固效果不够稳定。文献[11]提出,在逻辑综合时,将具有反相逻辑的门电路紧靠在与非门的下一级可以通过电荷共享,产生脉冲窄化效应来减弱SET产生的脉冲宽度和幅度。但是这样的加固方法严重依赖于粒子入射的角度,具有一定的随机性。文献[12]指出,首先对与非门的输出节点进行备份,然后通过C单元和加强网络进行加固,实现消除SET的目的。但是引入过多晶体管使得面积和功耗代价对标准单元来说是无法忍受的。总体上,目前对数字逻辑的加固方法可分为两类,一是在逻辑门的内部节点抑制电压翻转的幅度,二是在传播过程中消除SET的影响[13]。

针对现有加固方法中的不足,本文提出一种代价最小,但是加固效果显著的与非门结构。在分析了与非门的单粒子敏感性之后,提出了一种基于三阱工艺,上拉网络接法不变,将下拉网络中的NMOS管各自源极和衬底短接的电路结构。在不增加晶体管的数目和不影响电路逻辑状态的前提下,有效地提高了抗单粒子性能。

1 逻辑门中的单粒子瞬态当高能粒子轰击电路中的敏感节点时,产生大量电离的电子-空穴对,这些载流子定向移动使得输出节点的电压发生瞬间的跳变就形成了单粒子瞬态[14-16]。以反相器为例,见图 1,其中PMOS管使用Spice模型,而NMOS管采用经过工艺校准的三维器件结构。当电路的输入为“0”时,PMOS管导通,NMOS管截止,输出节点电容被充电,输出为“1”,此时NMOS管的漏极为敏感节点。

|

图 1 反相器单粒子瞬态仿真 Fig. 1 Simulation of SET in an inverter |

当高能带电粒子轰击敏感节点时,在粒子的路径上产生大量的电子-空穴对,使得漏-衬PN结瞬间穿通。在电场力和浓度梯度的作用下,空穴向偏置为低的衬底方向迁移,而电子向输出节点移动,造成输出节点的电势突然降低的现象。当粒子入射一段时间后,辐射产生的自由电子和空穴被完全复合,器件内部的电势便又恢复至轰击前的状态,电路正常工作[17-18]。

研究表明[19],在深亚微米工艺器件的SET响应中,辐射产生的脉冲电流逐渐从原来的双指数形式变成一种“平台”电流。这种转变机理是十分复杂的,与诸多因素相关。一方面,与器件中的体接触、阱接触的面积以及其到有源区的距离相关。当发生单粒子事件时,衬底中的电势在瞬间被置为统一的分布形式,此时电路中原有的漏结电压就被轻-重掺杂的衬底接触所俘获,因此该处的掺杂浓度和版图布局都决定着“平台”电流的持续时间。另一方面,按照摩尔定律下降的特征尺寸和电源电压实际上减弱了恢复管的驱动能力,而辐射产生的载流子浓度并没有随着器件同等下降,因此产生的辐射电荷定向移动形成的SET电流来不及被补偿或者泄放,造成了电流“平台”的产生[20-21]。

根据相关实验,在40 nm的CMOS器件中,LET值为10 MeV · cm2/mg的粒子产生的电流“平台”持续时间可以超过100 ps,该时间决定了SET电压的脉冲宽度。

2 电路设计基于N阱P衬工艺的数字集成电路设计中,MOS管往往被当作具有开关特性的三端器件。栅极电压控制源漏之间的通断,PMOS和NMOS管的阱和衬底则分别被偏置在统一的高、低电位。但是在目前工艺厂商提供的与双阱工艺兼容的三阱工艺中,P阱被衬底中的深N阱所隔离,可以进行独立偏置。前文分析了单粒子瞬态效应之后,本节提出将下拉网络中的NMOS管衬底与源极依次短接起来,最后一个NMOS管的衬底和源极同时连接到地。如果离输出节点最近的NMOS管栅极输入为“0”,则与非门的输出为“1”,其漏极为敏感节点。当发生单粒子瞬态时,产生的“平台”电流会在下面串联的NMOS管中产生一定的压降,使得衬底电势快速升高,从而阻碍空穴向衬底方向迁移,同时也减缓了电子向输出端移动的趋势,因此输出电压下降程度减缓,呈现出对单粒子轰击的鲁棒性。

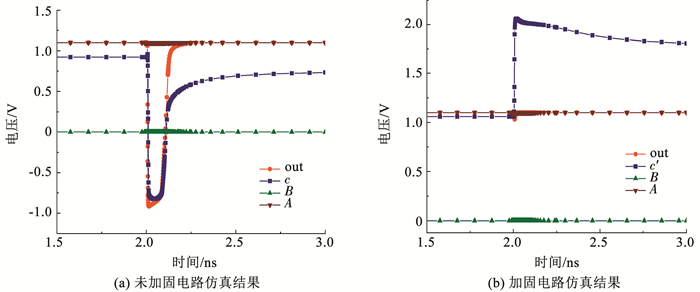

2输入与非门的线路结构,见图 2,其中N1管使用了三维NMOS模型。在未加固的电路中,将N1管和N2管之间的串联节点命名为c节点。类似地,加固结构中对应节点命名为c′。c节点的电容Cc可表示为

|

图 2 2输入与非门的混合仿真电路 Fig. 2 Hybrid simulation circuit of two-input NAND gate |

| $ C_c=C_{\mathrm{sj} 1}+C_{\mathrm{dj} 2} $ | (1) |

式中:Csj1是N1管源极总电容,包括一部分的栅源交叠电容和源-衬PN结电容;Cdj2为N2的漏极电容。在加固结构中,由于N1管的源衬短接,则c′节点的电容Cc′就只剩下Cdj2。因此,可以预见的是,加固的电路在一定程度上可以加快开关速度。

如果N2导通,因为导通电阻Ron的存在,使得“平台”电流在c′节点上产生一定的压降。通常在数字电路中,导通的NMOS管栅极控制信号为电源电压,由式(2)可知Ron的数值相对较小,这种情况下产生的c′节点电压上升是最小的,加固的效果也最差。因此将直接与输出节点相连的NMOS管关断,后续串联的所有NMOS管导通的输入信号称为“最坏”输入情况。可以合理推测,随着输入端口数目的增加,即使是这种输入条件下也能取得较好的加固效果。

| $ R_{\text {on }}=\frac{1}{\mu_{\mathrm{n}} C_{\mathrm{ox}} \frac{W}{L}\left(V_{\mathrm{GS}}-V_{\mathrm{TH}}\right)} $ | (2) |

如果N2关断,则c′节点的寄生电容同样可以加快N1衬底电位上升速度,抑制输出节点的翻转幅度。尤其是当节点电容减小之后,充电速度会更快,加强了抗单粒子翻转的性能。

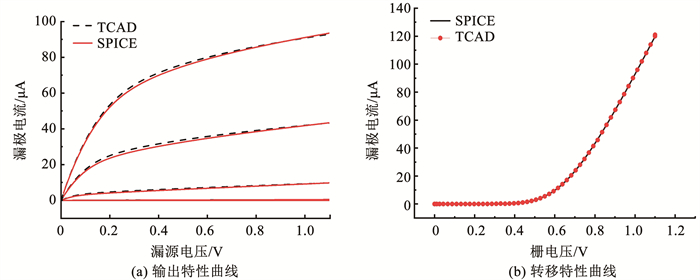

3 仿真结果与分析 3.1 实验设计为了验证提出的与非门的抗单粒子瞬态特性,本文使用Sentaurus TCAD仿真工具,基于40 nm工艺,构造出NMOS管的三维器件模型,并通过混合仿真的形式进行对比仿真实验。为保证实验的合理性,首先对构造的NMOS管进行工艺校准,校准结果见图 3。从图中可以看出,三维NMOS管的电学特性曲线能够和其Spice模型进行匹配,因此能够取代Spice模型进行粒子入射混合仿真实验。

|

图 3 器件的校准过程 Fig. 3 Calibration process of a device |

TCAD的优势在于能够最大程度地模拟实际电路中发生的辐射效应,可以仿真器件被轰击的实际物理位置和粒子入射角度以及LET值。本文采用重离子垂直入射N1管的漏极几何中心,即输出节点。利用高斯分布特性的电荷产生模型,轰击半径为10 nm,轰击起始时间为2 ns,LET值为10 MeV · cm2/mg[22]。

与图 2一致,每一组实验都采用传统与非门结构与提出结构对比的形式给出仿真结果。对于2输入与非门而言,根据图中器件的端口顺序——N1和N2的栅极信号分别记为A、B。输入情况共分为4种,分别是A=0、B=0,A=0、B=1,A=1、B=0以及A=1、B=1。不难发现,2输入与非门主要发生的是从“1”到“0”的翻转,占比为75%。如果能抑制该翻转,就能起到明显的加固效果。而且,随着输入端口数目的增加,输出结果中“1”的占比将会更多。因此,本文提出的加固方法是只针对从“1”到“0”的翻转,共3种输入情况。

3.2 加固效果分析 3.2.1 A=0、B=1图 4(a)为传统与非门输入信号分别为A=0、B=1时的单粒子瞬态仿真结果。该输入条件下,N1管的漏极为敏感节点。仿真结果显示,输出信号在2 ns时刻,发生了从“1”到“0”的翻转变化,输出电压从1.1 V跳变至-0.95 V,脉冲宽度为180 ps,而图 4(b)为加固的与非门受到单粒子轰击之后的翻转情况。从图中可以看出,当粒子入射之后,c′节点的电位被明显快速抬高,而输出节点翻转的最低值为0.13 V,和传统结构相比,电压翻转程度降低了55.6%,显著地改善了抗单粒子瞬态特性。尽管如此,这是2输入与非门中最坏的输入模式。实验结果表明,如果下拉网络中串联的管子数目增加,提出的电路结构即使在最坏情况下也能起到很好的抑制翻转效果。

|

图 4 输入为A=0、B=1时2输入与非门的单粒子瞬态 Fig. 4 SET in a two-input NAND gate when A=0 and B=1 |

上述现象产生的主要原因在于,未加固的电路中,N1和N2管的衬底统一被固定偏置到地。发生单粒子事件时,衬底和漏极端口吸引空穴和电子形成电压脉冲;而在加固电路中,N1衬底与源极短接,并连接到N2的漏极,此时SET电流产生的压降会使得c′节点的电势抬升,阻碍载流子的进一步定向迁移。图 4中的c和c′节点电势就反映了这一差异。

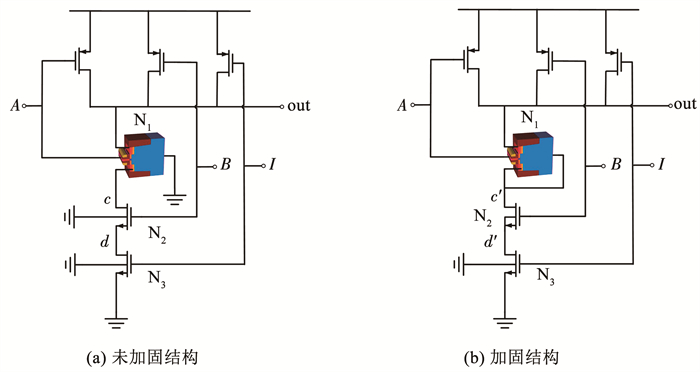

3.2.2 A=1、B=0对于与非门而言,当输入信号为“0”和“1”时,不论输入信号的顺序如何,输出的结果同为“1”。因此,为了验证加固之后的与非门对“01”输入有着同样的抗单粒子瞬态效果,需要对A=1、B=0的情况进行仿真。图 5(a)为未加固2输入与非门单粒子瞬态的仿真结果,图中显示输出节点仍然发生了明显的翻转,且最低电压值为-0.91 V。而在图 5(b)中,加固电路的输出节点几乎没有扰动,粒子轰击对输出电压没有影响。该现象的主要原因在于,当N1的源极和衬底短接到c′节点之后,辐射瞬间产生的大量空穴向衬底方向迁移的过程中,将c′节点被充至高电位,且远高于电源电压,快速阻断了空穴迁移的趋势,同时也遏制了电子向输出节点移动。由于最开始的电流是由漂移作用产生,响应速度快,大概在几个皮秒量级[23-24]。因此c′点电压上升速度极快,输出电压只是轻微扰动。该结构在本文的工艺和驱动能力下几乎实现了对单粒子瞬态完全免疫,其加固效果要比A=0、B=1条件下更加明显。总体来说,提出的与非门结构在两种输入顺序下都达到了抗单粒子翻转的作用,体现了输入“01”信号的对称性。

|

图 5 输入为A=1、B=0时2输入与非门的单粒子瞬态 Fig. 5 SET in a two-input NAND gate when A=1 and B=0 |

最后,仿真了输入信号为“00”时的加固效果。未加固与非门的单粒子瞬态仿真结果见图 6(a)。与前面的传统结构仿真结果相同,输出节点还是发生了大幅度的翻转,主要原因是衬底接地,对空穴还是具有很强的吸引作用,N1管的漏极吸引电子的能力未被减弱,因此输出节点出现了从“1”到“0”的翻转,最低电压为-0.87 V。而提出的与非门在输入为A=0、B=0条件下的单粒子仿真结果见图 6(b)。由图可知,当发生粒子轰击时,输出节点只是轻微扰动,没有翻转的现象。原因和前一种输入情况相同,轰击之后轻微的SET电流会瞬间提高衬底的电势,阻碍了空穴向衬底方向的流动,使得输出端收集的电子数目也相应减少,因此输出电压保持恒定。

|

图 6 输入为A=0、B=0时2输入与非门的单粒子瞬态 Fig. 6 SET in a two-input NAND gate when A=0 and B=0 |

以上仿真结果表明,提出的与非门结构对于不同输入条件下从“1”到“0”的翻转均有抑制的效果。尤其是在A=1、B=0和A=0、B=0时,抗单粒子的效果更加明显,电压几乎维持不变,在LET值为10 MeV · cm2/mg的条件下,实现了对单粒子轰击免疫的效果。

3.2.4 “最坏”情况下的3输入与非门根据前文所述原理,可以得出本文加固设计方法对多输入(3输入及以上)的与非门从“1”到“0”的翻转抑制效果将更为明显。最后,对传统的3输入与非门及其加固结构进行了粒子入射仿真实验。

提出的3输入与非门结构见图 7(b)。在2输入与非门的下拉网络中,增加了离输出节点最远的N3管,其栅极的输入被记为I,N2和N3的串联节点为d,加固结构中对应节点为d′。本次仿真是针对“最坏”输入情况进行的。N1、N2和N3管的输入信号分别为A=0、B=1、I=1。此时,N1管的漏极为敏感节点。粒子入射的条件与上面的实验中完全相同。

|

图 7 3输入与非门混合仿真电路 Fig. 7 Hybrid simulation circuit of a three-input NAND gate |

与2输入与非门的仿真结果相似,未加固的电路输出节点出现了大幅度的电压翻转,最低电压为-0.89 V, 见图 8。中间节点c、d电压也出现了不同程度的下降。对于加固的3输入与非门,其仿真结果和预期效果完全一致,电路的中间节点c′、d′电压分别被抬高,而且由于串联电阻的作用,c′节点的电势明显高于d′。输出节点电压仅仅从1.1 V下降至0.8 V。和加固前相比,即使在“最坏”输入情况下,3输入与非门的电压扰动降低幅度高达85.4%。如果以电源电压的一半作为高低电平的开关阈值来衡量,那么这样的波动实际上对逻辑值并未造成干扰,因此达到了抗单粒子瞬态的效果。

|

图 8 输入为A=0、B=1、I=1时3输入与非门的单粒子瞬态 Fig. 8 SET in a three-input NAND gate when A=0, B=1 and I=1 |

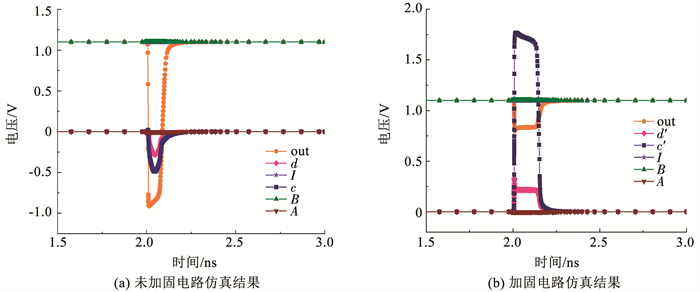

为了评估本文提出的加固方法,对2输入与非门的延时以及不同输入条件下的电压传输特性曲线进行仿真。在下面的仿真结果中,图例没有被标出来的输入信号表示一直处于逻辑高电平的状态。图 9(a)中标出来的信号表示正在发生从“1”到“0”的跳变,而图 9(b)中标出来的信号则表示相反的动作。

|

图 9 加固前后的延时对比 Fig. 9 Comparison of delay time before and after hardening |

从图 9中可以看出,加固对电路的上升和下降延时并未造成不良影响。反而在A=1, B从“1”到“0”跳变情况下,优化了上升延时;在A=1,B从“0”向“1”跳变过程中优化了下降延时。加固使得这一组延时同时减小,其他输入情况和原来保持相同。

与未加固结构相比,延时优化的根本原因在于加固电路中N1管和N2管串联节点处电容Cc′减小。在N1导通,N2逐渐关断的过程中,未加固的电路需要向电容Cc充电;同理,当N1导通,N2逐渐开启的过程中,需要对电容Cc放电,因此延时更大。而电路加固之后,电容Cc′和Cc相比,数值明显减小,因此延时更短。

加固前后的电压传输特性曲线见图 10,从图中可知,加固依然未对电路的电压传输特性造成影响。

|

图 10 加固前后的电压传输特性曲线 Fig. 10 Voltage transfer curves of NAND gate before and after hardening |

当A、B同时从“0”向“1”翻转时,由于上拉驱动能力最强,所以在很宽的电压范围内输出一直为高;而对于B=1,A从“0”到“1”翻转过程中,由于下拉管的漏源电压使得N1管的栅源电压减小,因此相比于A=1,B从“0”到“1”跳变的情况,电压传输特性曲线稍微向右移动。

5 结论本文分析了深亚微米集成电路的单粒子瞬态效应机理,并基于此提出了一种加固的与非门设计方法。提出的电路结构不仅功能正确,还在特定的输入情况下优化了上升和下降延时,而且不引入额外的器件。TCAD混合仿真实验表明,对于2输入与非门,在3种输入情况下都能起到抑制从“1”到“0”的翻转效果。尤其是在输入为A=1、B=0和A=0、B=0的2种情况几乎达到了对LET值为10 MeV · cm2/mg的单粒子效应完全免疫的效果。3输入与非门的仿真结果表明,该加固方法随着输入端数目的增加而效果更加明显。本文设计出的抗单粒子瞬态加固的与非门可以应用于基于三阱工艺的抗辐射标准单元库中。

| [1] |

CAI Chang, LIU Tianqi, ZHAO Peixiong, et al. Multiple layout-hardening comparison of SEU-mitigated flip-flops in 22-nm UTBB FD-SOI technology[J]. IEEE Transactions on Nuclear Science, 2020, 67(1): 375. DOI:10.1109/TNS.2019.2956171 |

| [2] |

赵元富, 王亮, 岳素格, 等. 纳米级CMOS集成电路的单粒子效应及其加固技术[J]. 电子学报, 2018, 10(10): 2516. ZHAO Yuanfu, WANG Liang, YUE Suge, et al. Single event effect and its hardening technique in nano-scale CMOS integrated circuits[J]. Acta Electronia Sinica, 2018, 10(10): 2516. DOI:10.3969/j.issn.0372-2112.2018.10.027 |

| [3] |

CHEN Jianjun, CHEN Shuming, HE Yibai. Novel layout technique for N-hit single-event transient mitigation via source-extension[J]. IEEE Transactions on Nuclear Science, 2012, 59(6): 2862. DOI:10.1109/TNS.2012.2212457 |

| [4] |

NARASIMHAM B, GAMBLES J W, SHULER R L, et al. Quantifying the effect of guard rings and guard drains in mitigating charge collection and charge spread[J]. IEEE Transactions on Nuclear Science, 2008, 55(64): 3457. DOI:10.1109/TNS.2008.2007119 |

| [5] |

JAGANNATHAN S, GADLAGE M J, BHUVA B L, et al. Independent measurement of SET pulse widths from N-hits and P-hits in 65-nm CMOS[J]. IEEE Transactions on Nuclear Science, 2008, 57(6): 3388. DOI:10.1109/TNS.2010.2076836 |

| [6] |

RAO R R, CHOPRA K, BLAAUW D T, et al. Computing the soft error rate of a combinational logic circuit using parameterized descriptors[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26(3): 472. DOI:10.1109/TCAD.2007.891036 |

| [7] |

DODD P E, MASSENGILL L W. Basic mechanisms and modeling of single-event upset in digital microelectronics[J]. IEEE Transactions on Nuclear Science, 2003, 50(2): 587. DOI:10.1109/TNS.2003.813129 |

| [8] |

ZHANG Ming, SHANBHAG N R. A CMOS design style for logic circuit hardening[C]// Reliability Physics Symposium Proceedings. [S. l. ]: IEEE, 2005. DOI: 10.1109/RELPHY.2005.1493088

|

| [9] |

LIN Dianpeng, XU Yiran, LI Xiaoyun, et al. A novel SEU tolerant memory cell for space applications[J]. IEICE Electron Express, 2018, 15(17): 660. DOI:10.1587/elex.15.20180656 |

| [10] |

DU Yankang, CHEN Shuming, LIU Biwei, et al. A constrained layout placement approach to enhance pulse quenching effect in large combinational circuits[J]. IEEE Transactions on Device and Material Reliability, 2014, 14(1): 272. DOI:10.1109/TDMR.2013.2291409 |

| [11] |

TOKALA V R, SANGEETA N. Single event transient hardening technique for logic gates based on radiation hardening by Reliability design[J]. International Journal of Electrical and Electric Engineering & Telecomunications, 2017, 6(2): 54. DOI:10.1109/ICPEICES.2017.7853538 |

| [12] |

HARMANDER S D, DENNIS S, DAVID B. Gate-level mitigation techniques for neutron-induced soft error rate[C]//Proceedings of the Sixth International Symposium on Quality Electronic Design. [S. l. ]: IEEE, 2005: 178. DOI: 10.1109/ISQED.2005.61

|

| [13] |

DING Lili, CHEN Wei, WANG Tan, et al. Modeling the dependence of single-event transients on strike location for circuit-level simulation[J]. IEEE Transactions on Nuclear Science, 2018, 66(6): 868. DOI:10.1109/TNS.2019.2904716 |

| [14] |

赵馨远, 张晓晨, 王亮, 等. 晶体管形状对单粒子瞬态脉冲特性的影响研究[J]. 微电子学与计算机, 2014, 31(10): 76. ZHAO Xinyuan, ZHANG Xiaochen, WANG Liang, et al. Impact of gate shape of transistor on single event transient pulse[J]. Microelectronics & Computer, 2014, 31(10): 76. |

| [15] |

LIU Zheng, CHEN Shuming, LIANG Bin. Analyse of current components in NMOS single event transient[C]// 2009 European Conference on Radiation and its Effects on Components and Systems. Brugge: IEEE, 2009: 246. DOI: 10.1109/RADECS.2009.5994587

|

| [16] |

SANDEEPAN D. Trends in single event pulse widths and pulse shapes in deep sub-micro CMOS[D]. Nashville: Vanderbilt University, 2007

|

| [17] |

BENEDETTO J M, EATON P H, MAVIS D G, et al. Digital single event transient trends with technology node scaling[J]. IEEE Transactions on Nuclear Science, 2006, 53(6): 3464. DOI:10.1109/TNS.2006.886044 |

| [18] |

QIN Junrui, CHEN Shuming, LIU Biwei. Research on single event transient pulse quenching effect in 90 nm CMOS technology[J]. Science China Technology Science, 2011, 54(11): 3066. DOI:10.1007/s11431-011-4579-6 |

| [19] |

CABANAS H, CANON E H, RABAA S, et al. Robust SEU mitigation of 32 nm dual redundant flip-flops through interleaving and sensitive node-pair spacing[J]. IEEE Transactions on Nuclear Science, 2013, 60(6): 4376. DOI:10.1109/TNS.2013.2288090 |

| [20] |

EBRAHIMI M, ASADI H, BISHNOI R. Layout-based modeling and mitigation of multiple event transients[J]. IEEE Transactions on Computer Aided Design and Integrated Circuits and System, 2016, 35(3): 369. DOI:10.1109/TCAD.2015.2459053 |

| [21] |

BUCHNER S P, FLORENT M, VINCENT P. Pulsed-laser testing for single-event effects investigations[J]. IEEE Transactions on Nuclear Science, 2013, 60(2): 1865. DOI:10.1109/TNS.2013.2255312 |

| [22] |

高成, 张芮, 王怡豪, 等. 深亚微米CMOS反相器的单粒子瞬态效应研究[J]. 微电子学, 2019, 10(49): 729. GAO Cheng, ZHANG Rui, WANG Yihao, et al. Study on single event transient in a deep submicron CMOS inverter[J]. Microelectronics, 2019, 10(49): 731. DOI:10.13911/j.cnki.1004-3365.180493 |

| [23] |

ANTONIO C, ANTONIO R, FRANCESC M, et al. Active radiation-hardening strategy in Bulk FinFETs[J]. IEEE Access, 2020, 30(3): 859. DOI:10.1109/ACCESS.2020.3035974 |

| [24] |

MUNTEANU D, AUTRAN J L. Simulation analysis of bipolar amplification in independent-gate FinFET and multi-channel NWFET submitted to heavy-ion irradiation[J]. IEEE Transactions on Nuclear Science, 2012, 59(6): 3256. DOI:10.1109/TNS.2012.2221740 |

2023, Vol. 55

2023, Vol. 55