坐标旋转数字计算机(Coordinate Rotation Digital Computer,CORDIC)是J.Volder于1959年提出的一种算法[1],这种算法通过一系列旋转角不断逼近目标角度,由移位相加迭代得到目标角度的正余弦值[2]. CORDIC算法具有硬件实现简单、速度快、精度可调等优点,在全数字锁相环、直接数字频率合成、快速傅里叶变换等领域有着广泛应用[3-6].传统的CORDIC算法采用流水线型结构[7],通过大量迭代来保证输出精度,因此存在硬件资源消耗过多、输出时延较长的问题.

随着现代数字通信系统集成化程度和精度的不断提高,许多学者对CORDIC算法提出改进方案.文献[8]提出一种贪婪搜索算法,采用跳过若干旋转角度和重复某些旋转角度的方法进行迭代,迭代次数有一定减少,但硬件复杂度明显增加.文献[9]采用一种混合结构,将旋转角度分为两部分处理,与传统流水线型CORDIC算法相比提高运算速度,但仍存在硬件消耗大、输出精度低的问题.文献[10]中的免缩放因子双步旋转算法免去缩放因子,减少迭代次数,但双步旋转的硬件实现结构较为复杂.文献[11]提出免缩放自适应CORDIC算法,虽然硬件资源消耗和误差有所减少,但是计算所需的时钟周期太长.文献[12-13]提出一种三阶段CORDIC算法,第一阶段通过查找表得到若干次迭代后的值,第二阶段采用移位相加的蝶形迭代运算,第三阶段进行合并迭代,相比于传统的流水线型CORDIC算法在精度和硬件消耗上都有一定改善,计算所需的周期少,具有一定代表性和优越性.

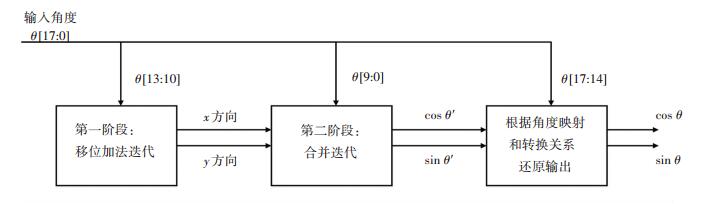

本文在文献[12-13]的基础上结合角度二极化重编码(Binary To Bipolar Recoding, BBR)、角度区间折叠、合并迭代等手段提出一种免查找表CORDIC算法,将三阶段缩减为两阶段实现.在典型的三阶段CORDIC实现方法基础上,将第一阶段的查找表直接替换为有限的几步移位相加迭代运算,有效减少寄存器消耗.此外,将第二阶段和第三阶段合并为一步迭代,大幅减少输出时延.用几步迭代运算代替查找表,使输出延时有所增加,但第二阶段的合并迭代只需要一个时钟周期,同时省去原有的蝶形运算阶段,整体只需要5个时钟周期就能得到输出结果,整体延时还有所降低.同时在综合采用角度二极化重编码和角度区间折叠技术后,改进算法的精度相比于传统实现方法也有一定改善.

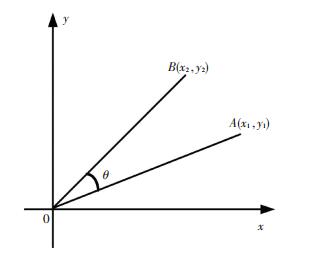

1 CORDIC算法基本原理CORDIC算法通过一系列旋转角不断逼近输入角度,由移位相加迭代得到输入角度的正余弦值. 图 1为向量旋转图,在平面直角坐标系中将初始向量OA=(x1, y1)逆时针旋转角度θ到向量OB=(x2, y2),则坐标之间的关系为

|

图 1 向量旋转示意 Figure 1 Rotation vector diagram |

| $ \begin{array}{l} \left[\begin{array}{l} {x_2}\\ {y_2} \end{array} \right] = \left[\begin{array}{l} \cos \theta \;\;\;\;\;\;-\sin \theta \\ \sin \theta \;\;\;\;\;\;\;\;cos\theta \end{array} \right] = \\ \cos \theta \left[\begin{array}{l} 1\;\;\;\;\;\;\;\;\;\;-\tan \theta \\ \tan \theta \;\;\;\;\;\;\;\;\;1 \end{array} \right]\left[\begin{array}{l} {x_1}\\ {y_1} \end{array} \right]. \end{array} $ | (1) |

将角度θ视为N个角度的累加和,即

| $ \begin{array}{l} \left[\begin{array}{l} {x_2}\\ {y_2} \end{array} \right] = \cos {\theta _{N - 1}}\cos {\theta _{N - 2}} \cdots \cos {\theta _0} \cdot \\ \left[\begin{array}{l} 1\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;-\tan {\delta _{N-1}}{\theta _{N-1}}\\ \tan {\delta _{N - 1}}{\theta _{N - 1}}\;\;\;\;\;\;\;\;\;\;1 \end{array} \right]\\ \left[\begin{array}{l} 1\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;-\tan {\delta _{N-2}}{\theta _{N-2}}\\ \tan {\delta _{N - 2}}{\theta _{N - 2}}\;\;\;\;\;\;\;\;\;\;\;1 \end{array} \right] \cdots \cdot \\ \left[\begin{array}{l} 1\;\;\;\;\;\;\;\;\;\;-\tan {\delta _0}{\theta _0}\\ \tan {\delta _0}{\theta _0}\;\;\;\;\;\;1 \end{array} \right]\left[\begin{array}{l} {x_1}\\ {y_1} \end{array} \right] = \\ K \cdot \left[\begin{array}{l} 1\;\;\;\;\;\;\;\;\;\;\;\;\;-\tan {\delta _{N-1}}{\theta _{N-1}}\\ \tan {\delta _{N - 1}}{\theta _{N - 1}}\;\;\;\;\;\;\;\;1 \end{array} \right] \cdot \\ \left[\begin{array}{l} 1\;\;\;\;\;\;\;\;\;\;\;\;\;-\tan {\delta _{N-2}}{\theta _{N-2}}\\ \tan {\delta _{N - 2}}{\theta _{N - 2}}\;\;\;\;\;\;\;\;1 \end{array} \right] \cdots \\ \left[\begin{array}{l} 1\;\;\;\;\;\;\;\;\;\;-\tan {\delta _0}{\theta _0}\\ \tan {\delta _0}{\theta _0}\;\;\;\;\;\;1 \end{array} \right]\left[\begin{array}{l} {x_1}\\ {y_1} \end{array} \right] \end{array} $ | (2) |

其中:K=cos θN-1cos θN-2…cos θ0称为校模因子,在N确定时可视为常数.令θi=arctan(2-i),在单次迭代时不考虑校模因子,那么有

对于取值为[0, π/8]的任意输入角度θ可用N位二进制小数示为

根据CORDIC算法的基本原理,可通过式(3)迭代得到输入角度的正余弦值

| $ \left\{ \begin{array}{l} {x_{k + 1}} = {x_k}-{r_k}\tan \left( {{2^{-k}}} \right){y_k}, \\ {y_{k + 1}} = {y_k} + {r_k}\tan \left( {{2^{-k}}} \right){x_k}. \end{array} \right. $ | (3) |

式中k代表迭代次数.

在三阶段CORDIC算法中,对于输出N位的CORDIC算法,当k < N/3时可利用上式(3)建立第一阶段的小容量查找表.当N/3≤k < N/2时,利用tan(2-k)≈2-k进行第二阶段的蝶形运算,当k≥N/2时进行合并迭代.本文提出的免查找表CORDIC改进算法将第一阶段中tan(2-k)用二进制小数近似,对于输出为16位小数的CORDIC算法,第一阶段用到的近似如式(4)所示.

| $ \left\{ \begin{array}{l} \tan \frac{1}{8} \approx {2^{-3}} + {2^{-11}} + {2^{-13}} + {2^{ - 15}} + {2^{ - 17}}, \\ \tan \frac{1}{{16}} \approx {2^{ - 4}} + {2^{ - 14}} + {2^{ - 16}}, \\ \tan \frac{1}{{32}} \approx {2^{ - 5}} + {2^{ - 17}}, \\ \tan \frac{1}{{64}} \approx {2^{ - 6}}. \end{array} \right. $ | (4) |

那么式(3)中乘以正切项就可视为移位相加运算,其中k=3对应的结构见图 2.

|

图 2 移位相加结构 Figure 2 Shifter-adder structure |

图 2中(a)和(b)分别代表式(3)中的两个子式.通过这种近似方法,将查找表替换为移位相加的蝶形运算结构,从而减少寄存器消耗.

对于输出为N位小数的CORDIC算法,当迭代次数k≥N/2时,可作tan(2-k)≈2-k的近似,那么上式(3)所示的迭代可写为

对于(π/8, π/4]内的角度,存在式(5)所示的三角函数关系式

| $ \left\{ \begin{array}{l} \sin \left( {\frac{\pi }{4}-\theta } \right) = \frac{{\sqrt 2 }}{2}\left( {\cos \theta-\sin \theta } \right), \\ \cos \left( {\frac{\pi }{4}-\theta } \right) = \frac{{\sqrt 2 }}{2}\left( {\cos \theta + \sin \theta } \right). \end{array} \right. $ | (5) |

通过上式(5)可将(π/8, π/4]内的角度折叠到[0, π/8]内,有

| $ \left\{ \begin{array}{l} \cos \theta = \frac{{\sqrt 2 }}{2}\left[{\cos \left( {\frac{\pi }{4}-\theta } \right) + \sin \left( {\frac{\pi }{4}-\theta } \right)} \right], \\ \sin \theta = \frac{{\sqrt 2 }}{2}\left[{\cos \left( {\frac{\pi }{4}-\theta } \right)-\sin \left( {\frac{\pi }{4}-\theta } \right)} \right]. \end{array} \right. $ | (6) |

从式(6)看出,只要得到[0, π/8]内角度的正余弦值,进行一次加减法运算和

| 表 1 角度映射和正余弦转换关系 Table 1 Angle mapping and sine/cosine transition |

将角度折叠到[0, π/8]可以省掉三阶段算法中第二阶段的蝶形运算过程,只需要进行第一阶段的移位相加迭代和第三阶段的合并迭代,随后根据角度映射和转换关系即可还原输出正余弦值.

3 算法实现对于三阶段算法,第一阶段是建立小容量查找表,将经过校模因子缩放后的横纵坐标值存放起来[15].向量旋转中初始坐标为(x0, y0)=(K, 0),其中K为校模因子且有:K=cos(φ0)·cos(2-3)·cos(2-4)·cos(2-5)···cos(2-N-1)那么经过逆时针旋转φ0后的坐标值为

|

图 3 程序整体结构 Figure 3 Program overall structure diagram |

| $ \frac{{\sqrt 2 }}{2} \approx {2^{-1}} + {2^{-3}} + {2^{-4}} + {2^{ - 6}} + {2^{ - 8}} + {2^{ - 14}} + {2^{ - 16}}. $ | (7) |

因此

用Verilog HDL语言对传统流水线型CORDIC算法,三阶段CORDIC算法和免查找表CORDIC算法进行具体实现,在相同输出位宽的前提下,选用Xilinx公司的xc7k325t-2ffg900型号FPGA,利用ISE14.2自带的XST工具进行电路综合,得到寄存器和LUTs消耗情况以及最大输出时延见表 2.

| 表 2 三种算法的寄存器和LUTs消耗、最大输出时延 Table 2 Register and LUTs consumption, maximum output delay for three algorithms |

寄存器的消耗主要取决于查找表的大小和迭代次数,最大输出时延与迭代次数有关.改进算法通过四次迭代替换查找表,又通过合并迭代减少大量的迭代,整体只需要5个时钟周期就能得到输出结果.比较三种算法使用的寄存器数量和最大输出时延可看出,改进算法使用的寄存器数量仅为流水线算法的25.58%,相比于三阶段算法节省了43.3%的寄存器消耗,最大输出时延相比于流水线型算法减少了68.75%.

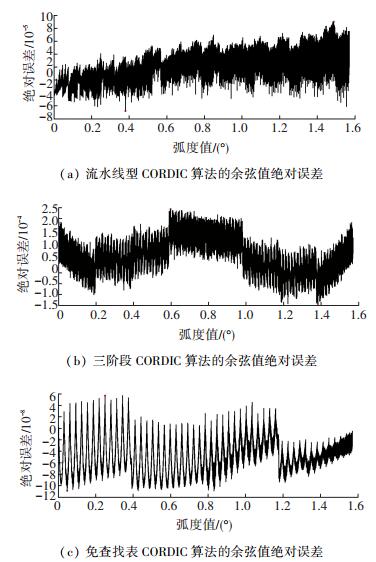

利用MATLAB对三种算法进行建模和误差分析,输入角度以2-15分辨率遍历[0, π/2],计算得到绝对误差. 表 3、4分别列出三种算法正余弦误差的最大值、最小值以及平均绝对误差值,其中三种算法的余弦值绝对误差如图 4所示,其中红色点代表的是绝对误差的最大值与最小值.通过比较三种算法的平均绝对误差值,可看出改进算法与流水线型算法的平均绝对误差处于同一数量级,但改进算法的平均绝对误差相对较小.和三阶段算法相比,改进算法的平均绝对误差相差一个数量级,其主要原因是在中间数据位宽较少时式(4)的近似误差较大,这一误差可通过采用更大的中间数据位宽来减小.

| 表 3 三种算法的正弦值误差 Table 3 Sine errors of three algorithms |

| 表 4 三种算法的余弦值误差 Table 4 Cosine errors of three algorithms |

|

图 4 三种算法的余弦值绝对误差 Figure 4 Cosine absolute errors of three algorithms |

针对传统流水线型CORDIC算法实现中存在的硬件资源消耗多、输出时延大等问题,结合角度二极化重编码、合并迭代以及角度区间折叠等技术提出了一种免查找表CORDIC算法.该算法将三阶段算法中的查找表替换为移位相加的迭代结构并省去了蝶形运算阶段,随后直接进行合并迭代,并根据角度映射关系还原输出结果.结果表明:与传统流水线型算法相比,免查找表算法的寄存器消耗减少了约74.42%,计算所需的时钟周期降低了68.75%.本文提出的免查找表CORDIC算法在实时性、输出精度、硬件资源消耗方面具有优势,适合高速实时的现代数字通信系统应用.

| [1] |

VOLDER J E. The CORDIC trigonometric computing technique[J].

IRE Transactions on Electronic Computers, 1959, EC-8(3): 330-334.

DOI: 10.1109/TEC.1959.5222693 |

| [2] |

AGGARWAL S, MEHER P K, KHARE K. Concept, design, and implementation of reconfigurable CORDIC[J].

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24(4): 1588-1592.

DOI: 10.1109/TVLSI.2015.2445855 |

| [3] |

DAS A, DASH S, BABU B C, et al. CORDIC algorithm based novel phase detection system for all digital phase locked loop[J].

Journal of Computational Intelligence& Electronic Systems, 2012, 1(1): 23-30.

|

| [4] |

KUMM M, KLINGBEIL H, ZIPF P. An FPGA-based linear all-digital phase-locked loop[J].

IEEE Transactions on Circuits & Systems Ⅰ: Regular Papers, 2010, 57(9): 2487-2497.

|

| [5] |

MEHER P K, VALLS J, JUANG T B, et al. 50 years of CORDIC: algorithms, architectures, and applications[J].

IEEE Transactions on Circuits & Systems Ⅰ: Regular Papers, 2009, 56(9): 1893-1907.

|

| [6] |

BOHER L, RABINEAU R, HELARD M. FPGAimplementation of an iterative receiver for MIMO-OFDM systems[J].

IEEE Journal on Selected Areas in Communications, 2008, 26(6): 857-866.

DOI: 10.1109/JSAC.2008.080803 |

| [7] |

HUANG Hai, XIAO Liyi. CORDIC based fast radix-2 DCT algorithm[J].

IEEE Signal Processing Letters, 2013, 20(5): 483-486.

DOI: 10.1109/LSP.2013.2252616 |

| [8] |

梁源, 王兴华, 向新, 等. 一种基于贪婪算法的CORDIC改进算法[J].

电讯技术, 2014, 54(3): 312-317.

LIANG Yuan, WANG Xinghua, XIANG Xin, et al. An improved CORDIC algorithm based on greedy algorithm[J]. Telecommunication Engineering, 2014, 54(3): 312-317. |

| [9] |

WANG Shaoyun, PIURI V, WARTZLANDER E E. Hybrid CORDIC algorithms[J].

IEEE Transactions on Computers, 1997, 46(11): 1202-1207.

DOI: 10.1109/12.644295 |

| [10] |

徐成, 秦云川, 李肯立, 等. 免缩放因子双步旋转CORDIC算法[J].

电子学报, 2014, 42(7): 1441-1445.

XU Cheng, QIN Yunchuan, LI Kenli, et al. Double-step scaling free CORDIC[J]. Acta Electronica Sinica, 2014, 42(7): 1441-1445. |

| [11] |

MAHARATNA K, BANERJEE S, GRASS E, et al. Modified virtually scaling-free adaptive CORDIC rotator algorithm and architecture[J].

IEEE Transactions on Circuits & Systems for Video Technology, 2005, 15(11): 1463-1474.

|

| [12] |

姚亚峰, 付东兵, 杨晓非. 基于CORDIC改进算法的高速DDS电路设计[J].

华中科技大学学报自然科学版, 2009(2): 25-27.

YAO Yafeng, FU Dongbing, YANG Xiaofei. Implement of high speed DDS circuit design using improved CORDIC algorithm[J]. Journal of Huazhong University of Science and Technology (Natural Science Edition), 2009(2): 25-27. |

| [13] |

MADISETTI A, KWENTUS A Y, WILLSON A N. A 100-MHz, 16-b, direct digital frequency synthesizer with a 100-dBc spurious-free dynamic range[J].

IEEE Journal of Solid-State Circuits, 1999, 34(8): 1034-1043.

DOI: 10.1109/4.777100 |

| [14] |

JUANG T B, HSIAO S F, TSAI M Y. Para-CORDIC: parallel CORDIC rotation algorithm[J].

IEEE Transactions on Circuits & Systems Ⅰ: Regular Papers, 2004, 51(8): 1515-1524.

|

| [15] |

牟胜梅, 李兆刚. 基于查找表和SF CORDIC的高精度正余弦函数求值方法[J].

计算机与数字工程, 2014, 42(3): 359-363.

MOU Shengmei, LI Zhaogang. A computation method of high-accuracy sine & cosine function based on lookup-table and SF CORDIC algorithm[J]. Computer & Digital Engineering, 2014, 42(3): 359-363. |

2017, Vol. 49

2017, Vol. 49