2. 中国科学院大学, 北京 100049

2. University of Chinese Academy of Sciences, Beijing 100049, China

DLL由于其结构简单,且抗PVT特性良好,广泛应用于时钟同步、时钟发生器等电路系统中[1-3].DLL的一个典型应用是DLL型90°移相器[4-5],可产生90°相移时钟,用于DDR SDRAM中,从而实现双倍数据率采样,在不改变时钟频率的条件下提高数据的传输速率.常见的DLL通过延时线来实现时钟的相移调节.延时线一般分为压控延时线[6]和数控延时线[7]两种.压控延时线是通过改变其栅电压实现延时调节;而数控延时线则是通过调整其数字控制信号以改变延时路径,从而实现延时调节.数控延时线结构简单,可全部由数字标准单元构成,不需要电容元件和电荷泵电路,易集成到数字电路系统中,面积也相对较小.但数控延时线是通过改变时钟信号(输入为时钟信号时)的延时路径来实现延时调节,因此在延时调节过程中会在输出端产生毛刺,这些毛刺可能会被相关的电路模块认为是时钟的上升沿或下降沿,从而导致使用该时钟的电路系统出现数据采样错误[8].

本文针对传统数控延时线出现的上述问题,提出了一种无毛刺数控延时线结构,该结构在传统与非门数控延时线的基础上增加了锁存器和时钟门控单元,使延时线数字控制信号的状态切换有序化,从而有效避免时钟毛刺的出现.提出的无毛刺数控延时线应用于DLL型90°移相器中,有效确保移相器在进行PVT跟随时,其输出的90°相移时钟不会产生毛刺.而且,该无毛刺数控延时线全部由标准单元构成,支持大规模数字电路设计流程,可用自动布局布线工具(如ICC)进行布局布线,能有效缩短设计周期.

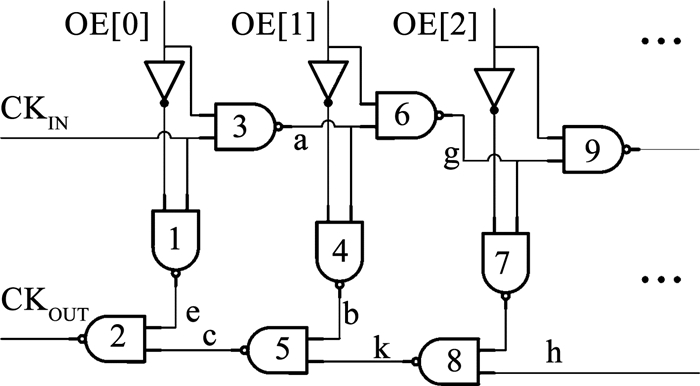

1 传统数控延时线图 1是文献[7]介绍的一种基于与非门的传统数控延时线.该延时线最小延时不受延时线长度的限制,因此被广泛应用于DLL,数控振荡器和时钟管理模块等电路结构中.该延时线的延时受数字信号OE[n:0]控制(n为整数,与延时线的级数相关).以前三级为例,当OE[2:0]=000时,CKIN通过与非门1和2,延时为2tNAND(tNAND为单级与非门的延时);当OE[2:0]=001时,CKIN通过与非门3、4、5和2,延时为4tNAND;当OE[2:0]=011时,CKIN信号通过与非门3、6、7、8、5和2,延时为6tNAND;更多级数的延时控制以此类推.

|

图 1 传统数控延时线 Fig. 1 Traditional DCDL |

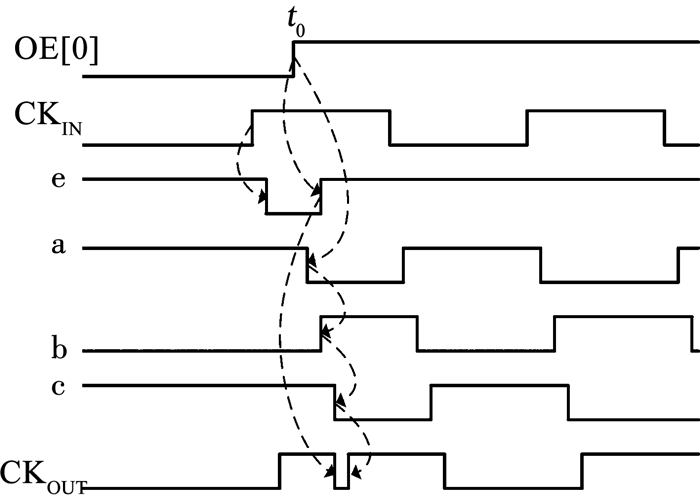

如图 2所示,以OE[2:0]从000切换到001为例分析时钟毛刺产生的原因.由于控制信号OE[2:0]切换时间不确定,该控制信号从000切换到001的过程中可能会导致时钟输出端CKOUT产生毛刺.出现毛刺的具体原因分析如下:在t0时刻,OE[0]从0跳变到1,经过一个非门和与非门1的延时后在节点e产生一个上升沿,此时,因为节点c为1,所以节点e的上升沿经过与非门2后在CKOUT端产生一个下降沿;另外,t0时刻OE[0]的上升沿经过与非门3的延时后在节点a生成一个下降沿,由于其他高位控制信号OE[2:1]均为0,节点a的下降沿通过与非门4、5、2在CKOUT端产生一个上升沿.由此可见,t0时刻OE[0]的上升沿经反相器和与非门1、2在CKOUT端生成的下降沿和经与非门3、4、5、2在CKOUT端生成的上升沿共同作用形成一个窄的时钟毛刺.由图 2可看出,毛刺的产生是OE[0]在节点CKIN为高电平时切换其状态导致的,因为在节点CKIN为高电平时,OE[0]的电平变化会通过与非门3和1传递到节点a和e并分别生成时钟沿,两个节点的时钟沿传递到CKOUT端导致毛刺出现.同理,如果OE[1]在节点a为高电平时切换其状态,也会导致毛刺出现.其他控制信号状态切换可依此类推.

|

图 2 传统数控延时线毛刺 Fig. 2 Glitch of traditional DCDL |

本文提出的无毛刺数控延时线需用到锁存器和时钟门控,因此本文先简单介绍锁存器和时钟门控.锁存器(latch)是数字电路中具有存储功能的逻辑元件[9], 它是一个电平敏感电路.如图 3(a)所示,在时钟信号为低电平时把输入D传送到输出端Q,此时锁存器处于透明(transparent)模式.当时钟跳变到高电平时,在时钟上升沿处被采样的输入数据在输出端保持稳定,此时锁存器处于维持(hold)模式.工作在这些情形下的锁存器被称为负锁存器,负锁存器及其时序如图 3(a)所示.同理,一个正锁存器在时钟信号为高电平时把输入D传送到输出Q,如图 3(b)所示.

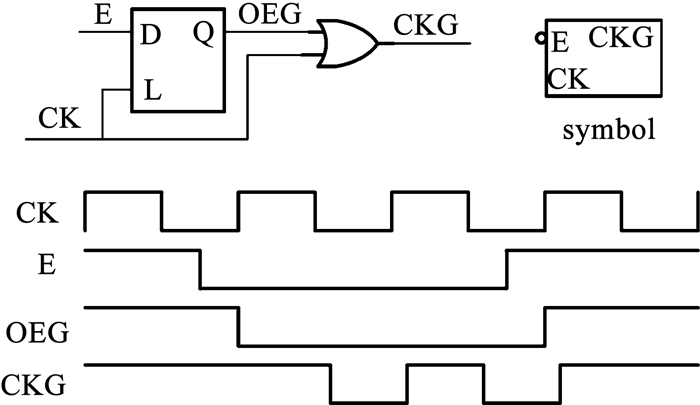

时钟门控[10]常用于时钟信号的开启和关断,以减小大规模数字集成电路的动态功耗,其电路和时序波形如图 4所示.简单的时钟门控由一个与门/或门就可以完全实现,但是时钟的使能信号E在0和1之间的切换时刻无法确定,可能会导致通过时钟门控后的时钟产生毛刺(glitch),造成时序逻辑电路功能错误.而基于锁存器的时钟门控可以很好地解决该时钟毛刺问题.如图 4所示,基于锁存器的时钟门控在上述或门时钟门控中加入了一个电平触发的锁存器.由时序图可见,锁存器只有在时钟处在高电平时为透明期,即在时钟为高电平时将E传输到Q端(OEG),因此OEG只有在CK为高电平时才会发生状态切换.而CK为高电平时,CKG恒为高电平,不受OEG状态切换的影响,因此E状态切换造成的毛刺被成功屏蔽.

|

图 4 时钟门控及其时序图 Fig. 4 Architecture and timing diagram of clock gating |

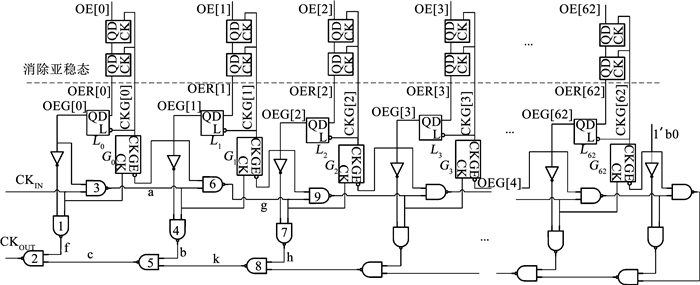

为解决毛刺问题,提出了图 5所示的无毛刺数控延时线(glitch free digitally controlled delay line, GFDL)结构.在传统数控延时线的基础上引入了寄存器,锁存器和时钟门控单元.由于数字控制信号OE相对于门控时钟CKG是异步信号,引入两级寄存器将OE与CKG同步以消除亚稳态,同步后输出为OER.信号OER经锁存器锁存后输出为OEG传递到延时线上.引入锁存器是为了保证控制信号OE的状态切换仅在延时线可能产生毛刺的节点(即CKIN,a,g,…)为0时才传递到延时线的延时控制节点(即OEG[0], OEG[1], OEG[2], …)上,避免因OE状态切换造成输出时钟出现毛刺.引入时钟门控主要是针对有多位OE信号同时由1切换到0的情形,时钟门控的使能端E连接后一级的OEG信号,可确保多位OE由1到0的状态切换是从高位到低位逐位传递到延时线的节点OEG上.

|

图 5 本文提出的无毛刺数控延时线 Fig. 5 The proposed glitch free DCDL |

以前三级延时调节为例,图 6(a)是GFDL的前三级数字控制信号OE[2:0]从000切换到011的时序图.在t0时刻,OE[2:0]从000切换到011.OE[0]跳变到1后经门控时钟CKG[0](时钟门控G0的输出时钟)触发的两级寄存器两拍采样后输出到OER[0]并使得OER[0]变为1.通过两拍采样得到的OER[0]与时钟CKG[0]上升沿同步并消除了亚稳态问题.OER[0]变为1后,在CKG[0]变为低电平时,触发锁存器L0将OER[0]锁存并使得OEG[0]跳变到1.从而将延时线的延时从△T0调整为△T1.因为L0只会在时钟CKG[0]为低电平时才会锁存OER[0]更新OEG[0]的值,由图 6(a)可知,CKG[0]为低电平锁存OER[0]时,CKIN也为低电平,此时,与非门1和3关断,使得与非门1和3的输出节点f和a恒为1,因此OEG[0]的值在CKIN为低电平时发生改变,不会传递到节点f和a,从而避免了因节点OEG[0]电平切换导致的毛刺.OEG[0]跳变到1后,延时路径从与非门1、2变成与非门3、4、5、2.时钟CKIN经过与非门3后传递到节点a,使节点a由恒1变为周期性时钟信号.由于OEG[2]为0,节点a的时钟可通过时钟门控G1传递到CKG[1],OE[1]经过CKG[1]的两个时钟上升沿同步后输出到OER[1],使得OER[1]由0变为1,然后,锁存器L1在节点CKG[1]变为低电平时,将OER[1]的值传输到节点OEG[1],使OEG[1]变为1.从而将延时线的延时从ΔT1调整为ΔT2.OEG[1]只在节点CKG[1]为低电平时才发生跳变,此时,节点a也为低电平,所以OEG[1]的变化不会传递到节点g和b上,从而有效避免毛刺.OEG[1]跳变到1后,一方面,关断时钟门控G0,使门控时钟CKG[0]变为恒1;另一方面,使延时路径从与非门3、4、5、2变成与非门3、6、7、8、5、2.时钟信号CKIN经过与非门3、6后传递到节点g,因此节点g由恒1变为周期性时钟信号.至此,OE的状态切换完全传递到节点OEG上,并成功避免毛刺的出现.

|

图 6 无毛刺数控延时线的时序图 Fig. 6 Timing diagrams of the glitch free DCDL |

图 6(b)是GFDL的前三级控制信号OE[2:0]从011切换到000的时序图.当OEG[1]为1时时钟门控G0是关闭的,其输出端CKG[0]恒为1.这是为了避免OEG[0]先于OEG[1]切换到0,切断节点a的时钟,导致OEG[1]无法切换到0.OE[2:0]在t0时刻从011切换到000,OE[1]经时钟CKG[1]两拍同步后输出到OER[1],使OER[1]变为0.信号OER[1]变为0后,在CKG[1]变为低电平时,锁存器L1将OER[1]的值传输至OEG[1],使OEG[1]切换到0.信号OEG[1]切换到0后,一方面关断与非门6开启与非门4,使得延时路径从与非门3、6、7、8、5、2变成与非门3、4、5、2,延时线的延时从ΔT2调整为ΔT1,与非门6的关断使得节点g由周期时钟信号变成恒1;另一方面开启了时钟门控G0,使得时钟CKIN传递到CKG[0].然后,OE[0]经时钟CKG[0]两个上升沿同步后输出到OER[0],使OER[0]变为0.信号OER[0]变为0后,在CKG[0]变为低电平时,锁存器L0将OER[0]的值传输至OEG[0],使OEG[0]切换到0.信号OEG[0]切换到0后,关断与非门3开启与非门1,使延时路径从与非门3、4、5、2变成与非门1、2,延时线的延时从ΔT1调整为ΔT0,延时调节完成.与非门3的关断使节点a由周期时钟信号变成恒1.

由上述分析可知,引入时钟门控G0和锁存器L0,使OEG[0]状态只在节点CKIN为低电平时切换,此时,与非门1、3关闭,能有效避免因OEG[0]状态切换产生毛刺;类似的,G1和L1使OEG[1]状态只在节点a为低电平时切换,此刻,与非门4、6关闭,也能有效避免因OEG[1]状态切换产生毛刺.其他OEG控制位的状态切换可以此类推.总而言之,引入时钟门控和锁存器,使延时线数字控制信号的状态切换有序化,有效解决了毛刺问题.

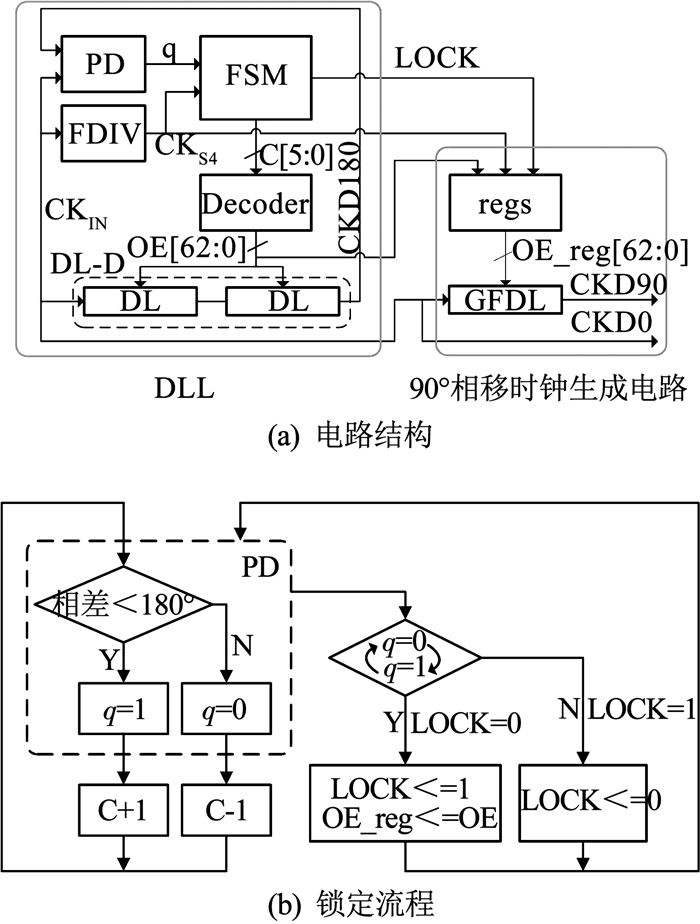

4 无毛刺DLL型90°移相器图 7是本文提出的无毛刺DLL型90°移相器(简称无毛刺移相器)结构,主要由鉴相器(PD)、分频电路(FDIV)、有限状态机(FSM)、译码器(Decoder)、传统数控延时线(DL)以及90°相移时钟生成电路构成.90°相移时钟生成电路采用本文提出的无毛刺数控延时线(GFDL),其延时是DLL级联反馈延时链(DL-D)的1/2.DLL根据输入时钟的频率调节DL-D的延时,使反馈时钟CKD180与参考时钟CKIN锁定在180°的相差上.DLL锁定后,GFDL就会产生90°相移时钟,该时钟可输送给相关电路模块如DDR数据接口电路使用.DDR双沿采样需要严苛的90°相移时钟,但是延时线易受PVT特性的影响使其延时产生较大波动.而在芯片内部,特别是大规模的数字集成电路芯片内部,PVT条件变化较大[7],延时线置于这样的工作环境中,其延时势必随PVT的变化产生较大波动.因此DLL锁定后,仍需进行PVT跟随调整.但是,由对传统数控延时线的分析可知,其延时调节过程可能会出现毛刺(glitch).这种短时间间隔的毛刺可能会被相关电路模块认为是一个时钟周期的开始,从而造成电路逻辑功能错误[8].因此,90°相移时钟生成电路模块采用了本文提出的无毛刺数控延时线(GFDL),确保该模块在跟随PVT调节的过程中不会产生毛刺;而DLL的反馈回路延时链(DL-D)仍由两级传统数控延时线(DL)构成,以减小面积开销.

|

图 7 无毛刺DLL型90°移相器及其锁定流程图 Fig. 7 Glitch free DLL supported 90°phase shifter and locking process |

传统DLL型90°移相器通常会锁定在360°相差上,并取该相差的1/4可得到90°相移时钟[4, 11].为了消除阻塞锁定并缩短延时线,本文的无毛刺移相器会锁定在180°相差上,并通过90°相移时钟生成电路复现180°相差的1/2值得到90°相移时钟CKD90.本文的无毛刺移相器工作原理如图 7(b)所示.FSM根据PD的鉴相结果通过调节控制码C对延时链DL-D的延时进行反馈调节,直到PD的输出q反复在1和0之间跳变,表示CKD180和CKIN的相差已经足够接近180°.FSM就会判定DLL进入锁定状态,将LOCK置1,同时将DL-D的控制信号OE存入寄存器组regs中以更新OE_reg的值,OE_reg控制GFDL生成90°相移时钟CKD90.当PVT发生较大变化时,CKD180和CKIN的相差较大地偏离180°相差,从而出现q在多个反馈调节周期内恒为0或1的情况,此时,FSM判定DLL失锁,将LOCK置0,并重新调整DL-D的延时,直到实现二次锁定,将LOCK重新置1,同时OE_reg也被同步更新,重新调整GFDL的延时,生成新PVT条件下的90°相移时钟.GFDL在延时调整过程中不会产生毛刺,可实时跟随新的PVT条件进行延时调节,而不影响其输出时钟CKD90在其他模块电路的使用.

5 物理实现及仿真结果本文使用SMIC65 nm CMOS工艺实现无毛刺移相器的设计.通过ICC自动布局布线得到如图 8所示版图.延时线的延时受元件位置和布线的影响,因此需要手工有序摆放,而FSM,寄存器组以及译码器等其他模块由于时序较宽松,可由ICC自动布局摆放即可.

|

图 8 版图设计 Fig. 8 Layout design |

图 9(a)、图 10(a)分别是系统时钟频率为1GHz,最慢PVT条件(即SS 1.08 V 125 ℃)下的前仿真和后仿真结果,无毛刺移相器锁定后,两路时钟CKD90和CKD0的相差分别为83.9°、81.9°,误差分别为6.78%、9.00%.因为SS 1.08 V 125 ℃的PVT条件下延时线的每一级步长达到最大,该PVT条件下,锁定频率能达到1 GHz,表明在其他PVT条件下锁定频率也能达到1 GHz.图 9(b)、图 10(b)分别是系统时钟频率为217 MHz,最快PVT条件(即FF 1.32 V-40 ℃)下的前仿真和后仿真结果,无毛刺移相器锁定后,两路时钟CKD90和CKD0的相差分别为87.7°、86.9°,误差分别为2.56%、3.44%.因为FF 1.32V-40℃的PVT条件下延时线的每一级步长达到最小,该PVT条件下,锁定频率能达到217 MHz,表明在其他PVT条件下锁定频率也能达到217 MHz.综上所述,提出的无毛刺移相器在介于最慢和最快的所有PVT条件下都能正常工作在217 MHz~1 GHz的频率范围内.

|

图 9 无毛刺移相器前仿真波形 Fig. 9 Pre-simulated results of the glitch free phase shifter |

|

图 10 无毛刺移相器后仿真波形 Fig. 10 Post-simulated results of the glitch free phase shifter |

后仿真是在前仿真的基础上,将版图的各节点寄生电阻、电容参数全部提出,并加入仿真.对比前仿真波形,由于增加了节点电阻电容,后仿真波形电平跳变的斜率有所增大,且在电平跳变处有小的电压过冲(如图 10(b)放大处所示).另外,由于节点电阻和电容的存在,后仿真90°相移时钟的相位误差稍微有所增大.

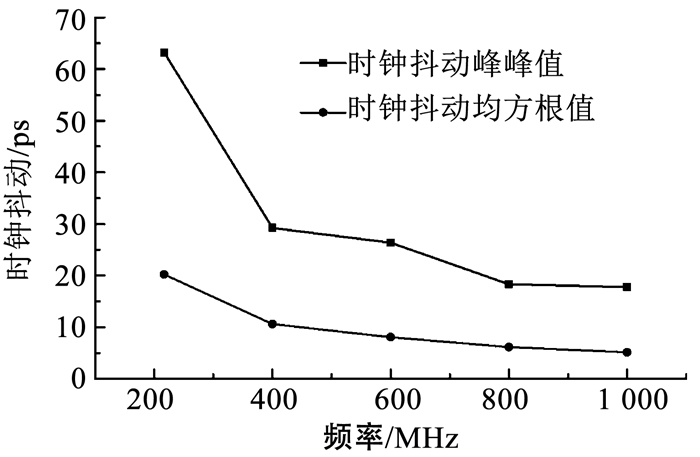

成熟稳压源(low dropout, LDO)电路可将电压波动控制在30 mV以内[12],因此本文在进行时钟抖动仿真时给电源电压添加了100 MHz 30 mV正弦波噪声,得到无毛刺移相器的输出90°相移时钟CKD90在各频率点的抖动峰峰值和均方根值,分别如图 11的两条曲线所示.1 GHz时,CKD90的抖动峰峰值和均方根值分别为17.77、5.16 ps.

|

图 11 各频率点下90°相移时钟抖动 Fig. 11 Simulated jitters of 90°shifted clock at different frequencies |

图 12为无毛刺移相器在SS,1.1 V,125 ℃的PVT条件下的电压跟随仿真波形,无毛刺移相器首次锁定后,在100 ns时刻VDD从1.1 V切换到1.3 V.无毛刺移相器因其反馈延时链(DL-D)的延时受该电压波动的影响而失锁.无毛刺移相器失锁后重新调节实现二次锁定并重新调整90°相移时钟,以减小其误差.通过对比仿真结果可知,90°相移时钟生成电路采用传统数控延时线(DL)时,二次调整会导致90°相移时钟CKD90DL出现毛刺;而采用本文提出的无毛刺数控延时线(GFDL)时,输出的90°相移时钟CKD90GFDL在二次调节过程中成功消除了毛刺.由此可见,本文提出的GFDL能有效抑制延时线数字控制信号状态切换导致的毛刺,使90°相移时钟生成电路中的延时线在工作过程中能实时进行电压等PVT特性跟随,解决了数控延时线因毛刺现象无法实时地进行PVT跟随调节的问题.

|

图 12 无毛刺移相器电压跟随仿真 Fig. 12 Simulation for voltage tracking of glitch free phase shifter |

移相器的另一个特性是希望无噪声干扰,波形完整,因此本文对移相器的输出90°相移时钟CKD90进行噪声仿真,移相器锁定在1 GHz和217 MHz时(PVT条件分别与图 10(a)、(b)一致),CKD90的噪声特性分别如图 13上侧和下侧所示,CKD90的噪声随其频率的增加而下降;移相器锁定在1 GHz和217 MHz时,在100 MHz频率点处的噪声功率密度分别约为4.874 6、3.568 0 nV2/Hz.可见,CKD90的噪声功率较小,可满足系统低噪声的要求.

|

图 13 输出时钟(CKD90)的噪声特性仿真 Fig. 13 Simulated noise of CKD90 |

本文设计的无毛刺移相器与其他文献的性能比较见表 1,提出的无毛刺移相器能有效消除时钟毛刺,且工作频率范围为217 MHz到1 GHz.具有无毛刺,工作频率范围宽、低电压、低功耗、高性能等特点.

| 表 1 移相器的性能比较 Tab. 1 Comparison of phase shifter performance with reference |

图 14是本文拟采用的测试方案,测试PBC板主要包含测试样片(test chip)、电源芯片(DC-DC, LDO)以及可编程FPGA芯片.测试仪器主要有电压源、信号发生器、恒温箱以及示波器.测试样片主要包含本文提出的无毛刺移相器,传统90°移相器和时钟管理模块(clk_gen).借鉴Yang等[13]给出的时钟方案,慢速时钟可通过片外的信号发生器提供,快速时钟可由片内的数控振荡器(DCO)[7]生成;片内外时钟通过选择器进行切换.通过对FPGA芯片进行编程,可生成测试样片的清零信号(nRst),clk_gen模块的控制信号(ctrlck, sel)以及电源芯片(DC-DC)的控制信号(ctrlp).测试过程将PBC板置于恒温箱中(而测试仪器在恒温箱外),时钟和观测信号用同轴电缆将其与相关测试设备相连,以减小信号的噪声干扰及衰减.

|

图 14 测试方案 Fig. 14 Measurement system for the test chip |

最高锁定频率的测试流程如下:clk_gen通过独立LDO芯片[14]单独供电,vdd_ck设计为1.2 V.类似的,采用LDO芯片给移相器模块供电,将vdd_core设定为1.08 V.同时将恒温箱的温度置为125 ℃.编程FPGA芯片调节ctrlck的值将DCO的输出时钟(ck)频率置为1 GHz,然后通过二选一选择器将ck选定为移相器的时钟输入.FPGA芯片通过nRst向移相器发出清零脉冲启动移相器工作.然后,通过示波器观察LOCK,CKD0和CKD90的波形并与图 10(a)对比.另外,通过测试多颗样片(test chip)的方法,来获取最慢的工艺角条件(P:SS).从而使上述测试条件很好的复现图 10(a)后仿真的最慢PVT(SS 1.08V 125℃)及时钟频率(1 GHz)条件.另一方面,最低锁定频率的测试流程如下:将vdd_core设定为1.32 V,并将测试温度设定在-40 ℃.通过信号发生器产生217 MHz时钟信号Ext ck,经片内二选一选择器将Ext ck选定为移相器的时钟输入.FPGA芯片通过nRst向移相器发出清零脉冲启动移相器工作.然后,可观察移相器的锁定情况以及输出时钟的相差.类似的,也需要测试多颗样片(Test chip),来获取最快的工艺角条件(P:FF).从而使测试条件很好地复现图 10(b)中后仿真的最快PVT(FF 1.32 V -40 ℃)及时钟频率(217 MHz)条件.

无毛刺特性的测试验证流程如下:温度设定为125 ℃且片外给定500 MHz的时钟信号.采用DC-DC芯片[15]对移相器模块供电.温度和频率设定好后,FPGA芯片通过调节控制信号ctrlp将电压初始值置为1.1 V,然后,FPGA芯片通过nRst向移相器发出清零脉冲启动移相器工作,移相器锁定后,FPGA芯片再次调节控制信号ctrlp将电压从1.1 V切换至1.3 V,通过示波器观察提出的无毛刺移相器和传统90°移相器的电压跟随调节波形是否与图 12中的仿真波形一致,从而验证所提出的无毛刺移相器的无毛刺特性.

时钟抖动和噪声测试可在移相器锁定后,分别用示波器和噪声分析仪对输出时钟信号(CKD90)进行测量即可.

7 结论1) 通过对传统数控延时线进行分析发现,传统数控延时线延时调节过程产生毛刺是由于其数字控制信号状态切换的无序性造成的.本文对传统数控延时线进行改进,提出了一种结合锁存器和时钟门控的无毛刺数控延时线,该数控延时线利用了锁存器和时钟门控的时序特性,使延时线数字控制信号的状态切换有序化,从而成功消除传统数控延时线的毛刺现象.

2) 将提出的无毛刺数控延时线集成到DLL型90°移相器中,并基于SMIC65 nm工艺进行设计以及仿真验证,HSPICE仿真发现,采用提出的无毛刺数控延时线时,DLL型90°移相器在进行PVT跟随调整过程中,输出的90°相移时钟不会产生毛刺;而采用传统数控延时线时,DLL型90°移相器在上述调整过程中,输出的90°相移时钟则会产生毛刺;从而有效验证了提出的无毛刺数控延时线具有消除传统数控延时线毛刺现象的特性.

3) 通过和已发表移相器的性能对比,表明了设计的无毛刺移相器具有无毛刺、锁定频率高、低电压、低功耗等优秀特性.此移相器可应用在DDR SDRAM物理接口,时钟管理模块等电路结构中,具有较高的实用性.

| [1] |

KIM Y S, LEE S K, PARK H J, et al. A 110 MHz to 1.4 GHz locking 40-phase all-digital DLL[J]. IEEE Journal of Solid-State Circuits, 2011, 46(2): 435. DOI:10.1109/JSSC.2010.2092996 |

| [2] |

HOYOS S, TSANG C W, VANDERHAEGEN J, et al. A 15 MHz to 600 MHz, 20 mW, 0.38 mm2 split-control, fast coarse locking digital DLL in 0.13 μm CMOS[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2012, 20(3): 564. DOI:10.1109/TVLSI.2011.2106170 |

| [3] |

HSIEH M H, CHEN L H, LIU S L, et al. A 6.7 MHz to 1.24 GHz 0.031 8 mm2 fast-locking all-digital DLL using phase-tracing delay unit in 90 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2005, 51(2): 412. DOI:10.1109/JSSC.2015.2494603 |

| [4] |

KANG H, RYU K, JUNG D H, et al. Process variation tolerant all-digital 90 phase shift DLL for DDR3 interface[J]. IEEE Transactions on Circuits and Systems-Ⅰ: Regular Papers, 2012, 59(10): 2186. DOI:10.1109/TCSI.2012.2188943 |

| [5] |

JUNG D H, RYU K, PARK J H, et al. All-digital 90° phase-shift DLL with dithering jitter suppression scheme[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2016, 24(3): 1015. DOI:10.1109/TVLSI.2015.2423312 |

| [6] |

MOON Y, KONG I, RYU Y, et al. A 2.2-mW 20-135-MHz false-lock-free DLL for display interface in 0.15-μm CMOS[J]. IEEE Transactions on Circuits and Systems Ⅱ: Express Briefs, 2014, 61(8): 554. DOI:10.1109/TCSII.2014.2327338 |

| [7] |

ANY J, JUNGD H, RY UK, et al. An energy-efficient all-digital time-domain-based CMOS temperature sensor for SoC thermal management[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23(8): 1512. DOI:10.1109/TVLSI.2014.2344112 |

| [8] |

HASAN SR, BELANGER N, SAVARIA Y, et al. Crosstalk-glitch gating: A solution for designing glitch-tolerant asynchronous handshake interface mechanisms for GALS systems[J]. IEEE Transactions on Circuits and Systems Ⅰ: Regular Papers, 2010, 57(10): 2696. DOI:10.1109/TCSI.2010.2046981 |

| [9] |

RABAEY J M, CHANDRAKASAN A, NIKOLICB. Digital integrated circuits: A design perspective 2nd ed[M]. London: Pearson Education, Inc., 2003: 300.

|

| [10] |

严石.面向DSP的时钟门控技术的优化与设计[D].南京: 东南大学, 2016 YAN Shi. Optimization and design of clock gating based on DSP[D]. Nanjing: Southeast University, 2016 http://cdmd.cnki.com.cn/Article/CDMD-10286-1016325847.htm |

| [11] |

ZHANG Dandan, YANG Haigang, ZHU Wenrui, et al. A multiphase DLL with a novel fast-locking fine-code time-to-digital converter[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2015, 23(11): 2680. DOI:10.1109/TVLSI.2014.2369460 |

| [12] |

HO M, LEUNG K N, MAK K L. A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages[J]. IEEE Journal of Solid-State Circuits, 2010, 45(11): 2466. DOI:10.1109/JSSC.2010.2072611 |

| [13] |

YANG P H, WANG J S. Low-voltage pulse width control loops for SOC applications[J]. IEEE Journal of Solid-State Circuits, 2002, 37(10): 1348. DOI:10.1109/JSSC.2002.803050 |

| [14] |

Texas Instruments. TPS74701 500-mA low-dropout linear regulator with programmable soft-start[EB/OL]. (2007-11)[2015-10].http://www.ti.com/lit/ds/symlink/tps74701.pdf

|

| [15] |

Texas Instruments. LM3370 Dual synchronous step-down dc-dc converter with dynamic voltage scaling function[EB/OL]. (2005-11)[2013-05]. http://www.ti.com/lit/ds/symlink/lm3370.pdf

|

2019, Vol. 51

2019, Vol. 51