2. 天津市成像与感知微电子技术重点实验室(天津大学), 天津 300072;

3. 天津大学 电气自动化与信息工程学院, 天津 300072

2. Tianjin Key Laboratory of Imaging and Sensing Microelectronic Technology (Tianjin University), Tianjin 300072, China;

3. School of Electrical and Information Engineering, Tianjin University, Tianjin 300072, China

在生物医学领域中,通常使用荧光物质标记待测样本,通过研究样本激发的荧光特性来分析样本及其所处环境的特征[1].传统的基于荧光强度的探测方法很容易受到激发激光强度、荧光染料溶度分布等因素的影响,难以做到定量测量[2].而荧光寿命则是绝对的,仅与样本自身特性和其所处的环境特性有关[3],因此荧光寿命成像(fluorescence lifetime imaging microscopy, FLIM)方法可以准确地获得待测样本的各项参数特征[4].

在荧光寿命成像中,通常使用TDC来精准地测量荧光信号的出现时间,TDC的性能直接关系到荧光寿命成像结果的优劣.为此许多学者对传统的TDC电路进行了改进.文献[5]中两级结构扩展了TDC的动态范围,但是二级TDC的抽头结构使其分辨率较低,而且受时钟频率的限制,其转换速率较低.文献[6]提出了一种多相位时钟的TDC,通过抽头延时线对锁相环产生的8个不同相位的参考时钟进行采样,虽然多相位时钟的稳定性使TDC的测量误差较小,但是其分辨率较低,动态范围难以提升.文献[7]给出了一种基于反相器的环形TDC,环形结构实现了较大的动态范围,但由于反相器对信号的上升沿和下降沿存在延时差异,使信号在传输过程中产生了较大的误差.文献[8]所描述的游标型结构利用两个延时大小相近的延时单元实现了亚门级的分辨率,但是游标结构存在有动态范围难以扩展和延时单元之间匹配难度大的问题.

为解决上述问题,本文提出了一种两级结构的TDC,第1级TDC利用计数型结构实现了大的动态范围;第2级TDC采用了一种优化的三通道游标结构,缩短了单条延时链的长度,降低了测量的不确定度.其中,采用差分结构的延时单元,有效提高了TDC的抗干扰能力;采用真单相时钟触发器(true single phase clocked, TSPC)作为D触发器,保证尽可能小的建立保持时间,进一步提高了TDC的测量精度.在两级结构TDC的基础上,结合SPAD、淬灭电路、存储读出电路搭建了一款可以应用于荧光寿命成像的单光子探测系统.

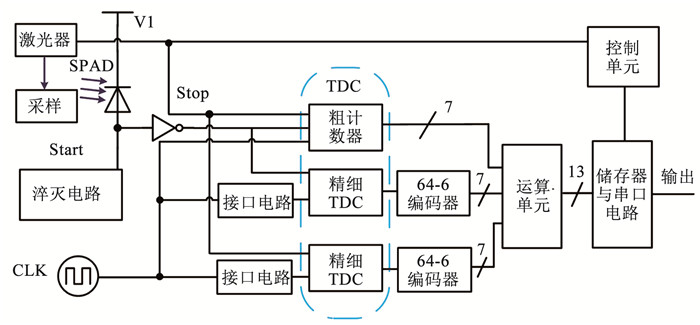

1 系统结构图 1为本文提出的单光子探测系统.其主要由SPAD、淬灭电路、前端接口电路、TDC电路、编码电路、存储读出电路等部分组成.SPAD工作在盖革模式下,感应荧光光子并产生雪崩脉冲,淬灭电路完成SPAD的淬灭和复位,并将雪崩信号经过反相器转化为数字脉冲,读入TDC[9].TDC电路连续测量荧光光子的出现时间,并将结果暂存在地址和时间相对应的存储器中.第1次探测开始之后,控制单元开始计时,当计时达到预设值时,结束荧光光子的探测,并控制串口电路将存储器的数据按地址顺序读出到上位机,得到荧光光子在时间上的概率分布直方图,通过算法还原得到待测样本的荧光寿命[10].

|

图 1 单光子探测系统框图 Fig. 1 Single photon detection system block diagram |

考虑到需要探测的荧光信号非常微弱,SPAD在每个探测周期能够探测到荧光光子的概率远小于1[11],这会导致TDC在多个探测周期内接收不到停止信号,浪费功耗.为此,本系统采用了反转启停的处理:将TDC的START信号和STOP信号对调,使SPAD生成的雪崩脉冲作为TDC的START信号, 而相邻周期的激光脉冲信号作为STOP信号,确保TDC电路只有在探测到光子后才工作,降低了系统功耗.

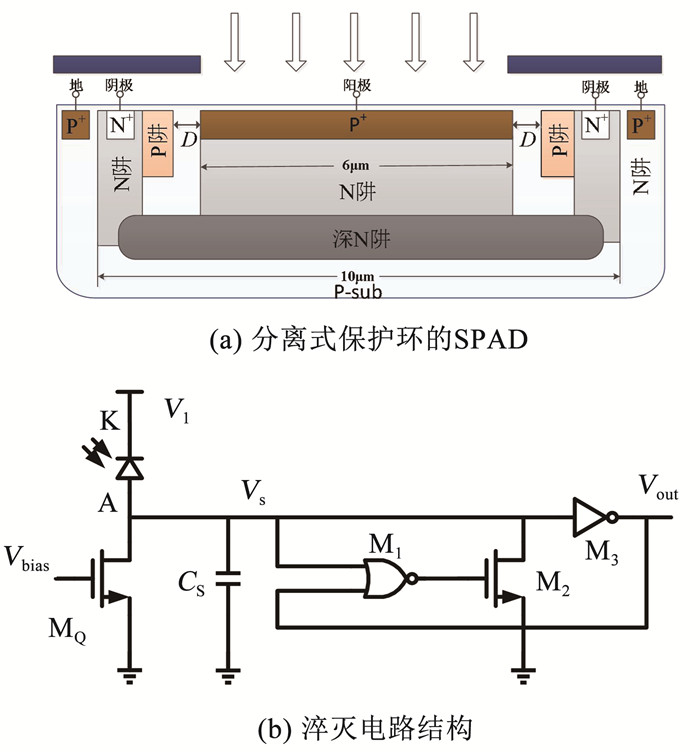

2 电路设计 2.1 SPAD和淬灭电路的结构在进行荧光光子探测时,SPAD两端的反偏压大于其反向击穿电压.为保护SPAD不发生边沿击穿,需要在其感光区周围添加保护环,并将SPAD的版图设计为正八边形以增大曲率半径,防止出现边缘击穿[12].本文采用了本实验室所设计的一种感光区和P阱保护环分离的SPAD,其结构如图 2(a)所示[13].

|

图 2 SPAD和淬灭电路 Fig. 2 SPAD and quenching circuit |

该器件主要由P+、Pwell、N+、Nwell、Deep Nwell和P-sub组成.其中P+、Nwell组成了雪崩pn结,是器件的感光区,P+引出电极作为器件的阳极;Pwell是SPAD的保护环,和感光区的间隔为D;Nwell将倒置掺杂的Deep Nwell包围,从N+引出电极作为器件的阴极.当器件工作时,Deep Nwell和P-sub处于反偏状态,使阳极和衬底相互独立.除感光区外,其他部分都用金属覆盖,以降低像素间的串扰[14].

淬灭电路完成SPAD的淬灭、复位和雪崩信号的输出.传统的被动淬灭电路结构简单,淬灭时间极短,但是复位时间很长,导致死时间长,探测效率低;主动淬灭电路性能优异,但电路结构复杂,功耗面积较大[15].所以本系统采用了一种被动淬灭-主动复位的淬灭电路实现了较小的探测死时间.电路结构如图 2(b)所示.

电路的工作原理为:1)准备阶段. MQ导通,SPAD两端电压为V1,大于其反向击穿电压,SPAD准备探测荧光信号;2)淬灭阶段. SPAD探测到荧光信号发生雪崩,产生一个流过MQ的雪崩电流,MQ分压使SPAD两端反向偏压降底,雪崩淬灭;3)主动复位. Vs通过Cs到MQ这一支路以斜率为I0/Cs的速度放电,I0为流过MQ电流的大小,设置或非门M1的阈值电压Vth1大于反相器M3的阈值电压Vth2,当Vs小于Vth1而大于Vth2时,M1输出高电平使M2导通,Vs迅速降为0 V,完成SPAD的复位.Vs从最大值降到Vth1的这段时间为淬灭电路的保持时间,其大小为

| $ {T_{{\rm{off }}}} = \frac{{{C_{\rm{S}}} \times \left( {{V_{{\rm{s}}, \max }} - {V_{{\rm{th}}1}}} \right)}}{{{I_0}}}, $ |

可以通过调整CS的大小来实现不同的保持时间,从而有效地抑制SPAD后脉冲的产生.

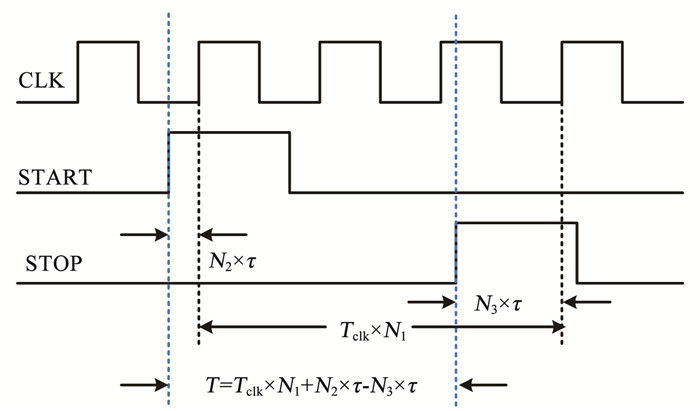

2.2 时间数字转换器本系统采用一种两级结构的TDC测量荧光信号的出现时间,测量原理如图 3所示.第1级计数型TDC测量START和STOP之间的时钟周期个数,输出为N1.两个二级TDC测量未满一个周期的时间余量,经过编码电路输出温度码最后一个1的位置,分别为N2和N3.二级TDC的动态范围需要和一级TDC的时间分辨率匹配,本文中二级TDC共64级,分辨率为τ,时钟周期为Tclk,则最终测得的时间间隔可以表示为

| $ T = {T_{{\rm{clk }}}} \times {N_1} + {N_2} \times \tau - {N_3} \times \tau = \left( {64 \times {N_1} + {N_2} - {N_3}} \right) \times \tau . $ |

|

图 3 两级TDC的测量原理 Fig. 3 Measurement principle of two-stage TDC |

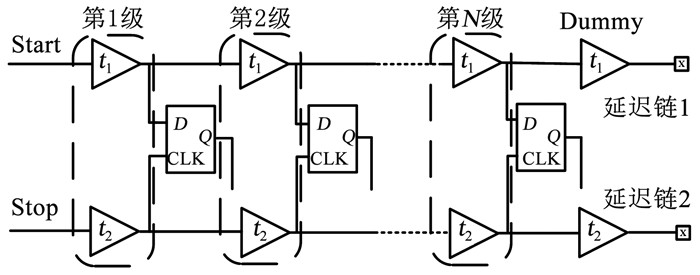

传统游标型TDC电路结构如图 4所示[16].START信号和STOP信号各自沿延时链1和2传播.其中,延时链1中延时单元的大小为t1,延时链2中延时单元的大小为t2,且t1>t2,故每经过一级延时单元,START信号和STOP信号的相位差会缩小t1-t2.STOP信号通过D触发器对START信号采样,得到一组从1变为0的温度码.假设待测的时间间隔为T,温度码的最后一个1出现在第n级,则有

| $ n \times \left( {{t_1} - {t_2}} \right) \le T < (n + 1) \times \left( {{t_1} - {t_2}} \right). $ |

|

图 4 传统游标延时链结构 Fig. 4 Traditional cursor delay chain structure |

由于PVT和环境噪声的影响,各级的延时差值会有一定的偏差.假设第i级延时单元的延时差值的偏差为μi,则第i级延时单元的延时差tres, i为

| $ {t_{{\rm{res}},i}} = \left( {{t_1} - {t_2}} \right) + {\mu _i} = {t_{{\rm{res}}}} + {\mu _i}, $ | (1) |

所以T近似为

| $ T = n \times {t_{{\rm{res}}}} + \sum\limits_{i = 1}^n {{\mu _i}} , $ | (2) |

而每级延时差的标准差相同,其大小为

| $ {\mathop{\rm std}\nolimits} \left( {{t_{{\rm{res}},i}}} \right) = {\mathop{\rm std}\nolimits} \left( {{\mu _i}} \right) = {\mathop{\rm std}\nolimits} (\mu ), $ | (3) |

则时间间隔T的不确定度为

| $ {\mathop{\rm std}\nolimits} (T) = {\mathop{\rm std}\nolimits} (\mu ) \times \sqrt n . $ | (4) |

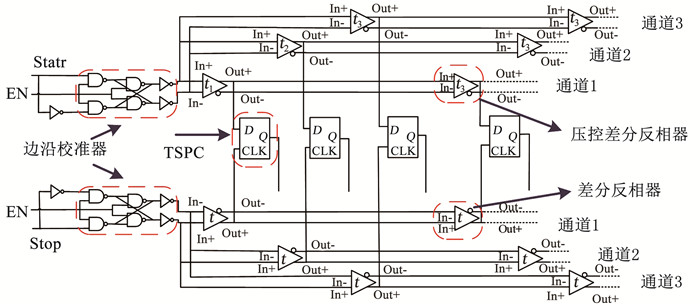

由式(4)可知,提高单级延时单元的抗干扰能力和缩短延时链的长度都可以降低测量结果的不确定度.基于此原理,本系统的二级TDC采用了一种基于压控差分反相器的三通道游标结构,如图 5所示.三通道的架构使得单条延时链的长度缩短为原来的1/3,差分结构的延时单元具有较强的抗干扰能力.由式(4)可知,测量结果的不确定度降低为传统结构的57%以下.

|

图 5 基于压控差分反相器的三通道游标TDC Fig. 5 Three-channel vernier TDC based on voltage-controlled differential inverter |

其中,下边3条延时链中延时单元的延时值固定为t,其结构如图 6(a)所示.上边3条延时链中延时单元的延时值为压控可调,其结构如图 6(b)所示,通过调整M5、M8的栅极控制电压,使得延时大小满足t1-t=30 ps、t2-t=60 ps、t3-t=90 ps,从而二级TDC实现了30 ps的时间分辨率.若延时单元的差分输入信号存在相位差,则会出现左右两条支路同时导通的情况,使延时单元的输出为不定态,增大TDC不确定度的同时也增大了功耗.为此在TDC中添加了边沿校准模块Edge aligner,为差分延时单元提供零相位差的差分输入信号,最大限度的消除了这种竞争冒险现象.

|

图 6 延时单元和D触发器的电路结构 Fig. 6 Circuit structure of delay unit and D flip-flop |

采用TSPC触发器判定START和STOP信号的相位关系,其电路结构如图 6(c)所示.TSPC触发器为单时钟控制,由M1、M2、M3组成的第1级反相器的延时为触发器的建立时间,M4、M5、M6组成的第2级反相器的延时为保持时间,通过调整MOS管的参数,使触发器的建立保持时间尽可能得小,从而提升触发器对START和STOP信号相位关系判断的灵敏度,提升TDC的测量精度.

2.3 前端接口、编码和存储读出电路由TDC的工作原理可知,二级TDC将CLK信号作为停止信号来测量不足一个时钟周期的时间余量.在延时链的级数比较大时,单条延时链的延时值可能会大于时钟周期,使输出的温度计码包含了多个时间间隔的信息.为此,需要将紧邻START信号或STOP信号上升沿的下一周期时钟上升沿提取出来,作为二级TDC的STOP信号.

每次测量结束之后,编码电路将二级TDC输出的温度码转换成二进制码,并产生一个高电平的使能信号.一级TDC每次测量结束后也会产生一个高电平的使能信号.只有当使能信号都为高时,才会计算最终的时间间隔T.

存储电路对地址进行编码,使地址和荧光信号出现的时间相对应,具体为每16 ps对应一个地址,即0~15 ps对应MEM[0],16~31 ps对应MEM[1],以此类推.TDC每测得一个荧光信号出现的时间,存储器对应地址的存储单元计数加一.测量一段时间后,串口电路按地址顺序将存储器的数值读出到上位机中,得到荧光光子在时间上的概率分布直方图.

3 仿真结果与分析在图 1中,淬灭电路、边沿对准模块和二级TDC采用全定制设计思路,以保证电路的性能和版图布局的合理;第1级TDC和其他电路模块采用RTL到GDS的半定制设计思路,降低设计难度.整个系统基于TSMC 0.18 μm CMOS混合信号工艺实现.

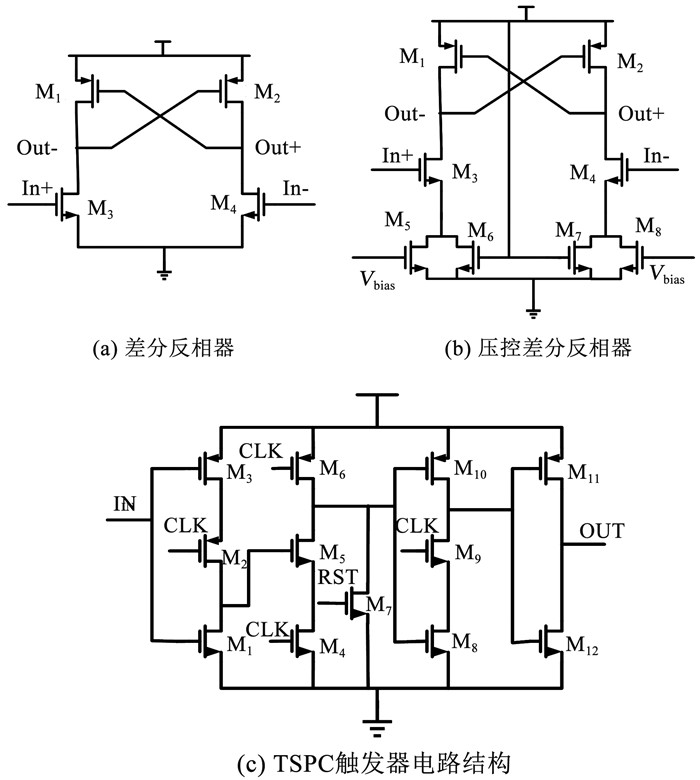

3.1 SPAD性能仿真基于TSMC 0.18 μm工艺绘制了图 2中SPAD的版图,在满足DRC规则的条件下,尽可能使其面积最小,同时为了防止边缘击穿,将SPAD的版图绘制为正八边形,如图 7(a)所示.

|

图 7 SPAD的版图和性能仿真结果 Fig. 7 SPAD layout and performance simulation results |

考虑到该器件主要用于荧光探测,所以仿真时设定入射光波长为荧光的典型波长480 nm,根据版图中SPAD的尺寸,在silvaco中进行了光暗电流的仿真,并根据仿真结果搭建SPAD的等效电路模型,结果如图 7(b)、图 7(c)所示.

由图 7(b)可以看出,SPAD器件的雪崩击穿电压大约为11.3 V,器件未发生雪崩时,暗电流在10-11 A以下,光电流约为10-8 A,比暗电流大3个数量级.当SPAD发生雪崩之后,雪崩电流在10-3 A以上,由于空间电荷效应,雪崩电流趋于饱和.

在图 7(c)中,R1是SPAD导通时的串联电阻,CD是感光区p-n结的等效电容,CPK和CPA分别为阳极、阴极和衬底的寄生电容.根据图 7(b)所示的仿真结果调整电流源的值,使从A点输出的电流大小为10-3 A,模拟SPAD的雪崩电流.

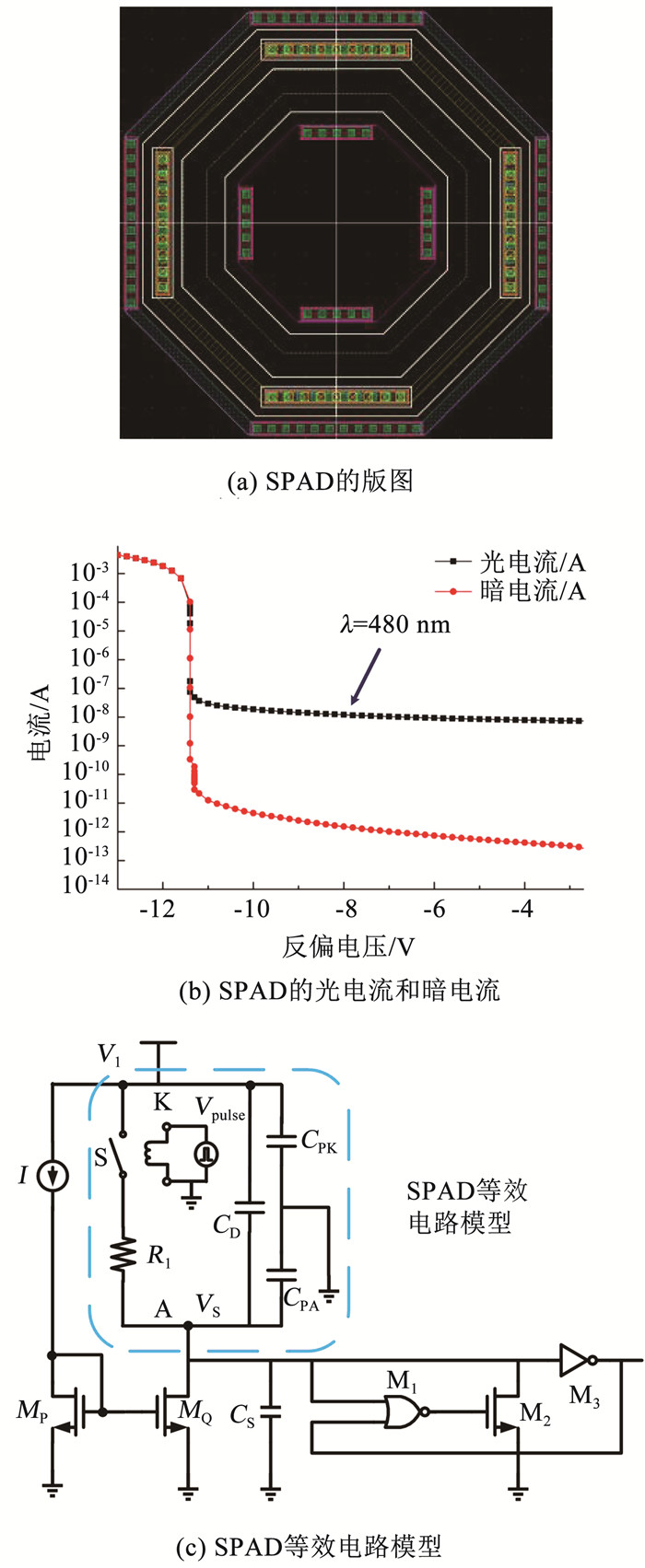

3.2 半定制模块仿真一级TDC、前端接口、编码、存储和串口读出电路等模块使用Verilog HDL语言描述,并在TSCM 0.18 μm CMOS工艺下进行物理实现,通过提取版图的寄生参数,将延时文件(.sdf)反标到电路网表(.v)基于VCS进行后仿真.后仿真结果如图 8所示.

|

图 8 半定制电路后仿真结果 Fig. 8 Post-simulation results of semi-custom circuit |

图 8(a)中,Q1[63:0]和Q2[63:0]为外加激励,模拟二级TDC输出的温度码;clk_out1和clk_out2为CLK信号经过前端接口电路后的输出;encode1、encode2和encode3为编码电路和一级TDC完成温度码的转换和时钟周期的计数后产生的使能信号,当这3个使能信号均为高电平,即encode为高电平时,计算最终时间间隔T,输出为T_final[12:0].

由仿真结果图 8(b)可以看出,当控制单元计时达到预定值之后,结束荧光信号的探测,并产生高电平的data_out_en,串口电路由CLK的分频时钟控制,将存储器中的数据以19 200 bps的速度读出,当控制信号start为高时,开始传输,按照串口通信协议,分别输出低电平的起始位和8 bit数据位(这里没有设置奇偶校验位),当clear信号有效时,结束一个数据的传输.串口输出端口为Serial_out,半定制电路功能符合设计要求,可以正常工作.

3.3 二级TDC仿真为保证二级TDC的精度,在版图绘制时,需要将3个通道及延时单元做成完全对称的,以保证每级的连接路径完全相同.版图采用1、2、3级交替排列的布局方式:通道1的第1级延时单元的输出跨过通道2和通道3的第1级延时单元输入到通道1的第2级延时单元中,以此循环.这种布局方式在保证了对称性的同时,最大程度压缩了版图的面积.

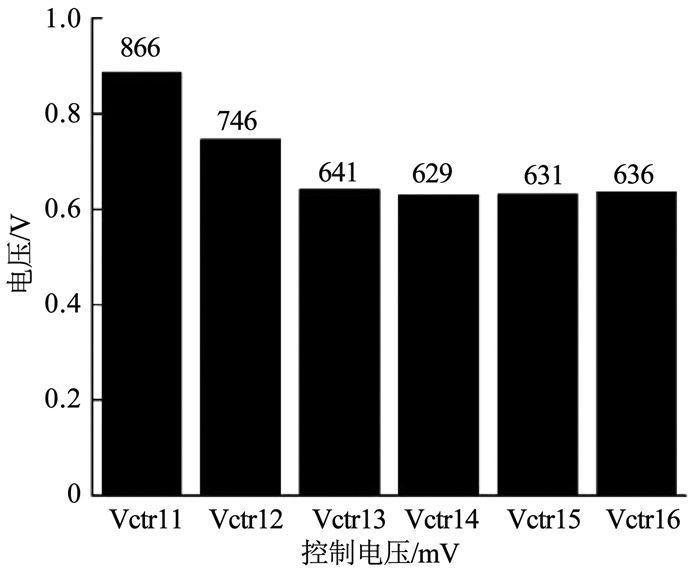

为消除工艺偏差和电压降的影响,压控差分延时单元由6个电压控制,其中Vctrl1控制第1级延时单元的延时大小,Vctrl2控制第2级延时单元的延时大小,Vctrl3-5分别控制第3~18级、19~34级、35~50级、51~64级的延时大小.通过调整Vctrl1-Vctrl6控制电压的大小,使得TDC能够实现30 ps的时间分辨率,Vctrl1-6的大小如图 9所示.其中,第1级延时单元的控制电压最大,实现30 ps的延时差;第2级延时单元需要保证延时差大小为60 ps,所以其控制电压次之;其余延时单元只需保证90 ps的延时差,其控制电压在同一工艺角下相差在15 mV以内.

|

图 9 工艺角tt下的控制电压 Fig. 9 Control voltage at process corner tt |

对版图提取寄生参数进行后仿真,输入0~1 920 ps均匀分布的时间间隔,通过分析温度码从1~0的变化位置即可得到二级TDC的测量结果,见表 1.其中第3、6、9组实验由于待测时间间隔为30 ps的整数倍,会导致START和STOP信号在某时刻上升沿重合,无法满足TSPC触发器的建立保持时间,导致触发器进入了亚稳态,其余时间间隔测量正确,TDC可以实现30 ps的分辨率.

| 表 1 二级TDC后仿真结果 Tab. 1 Secondary TDC simulation results |

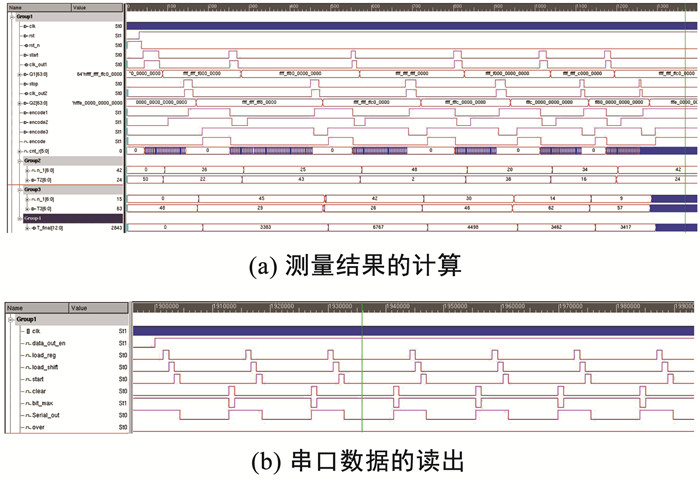

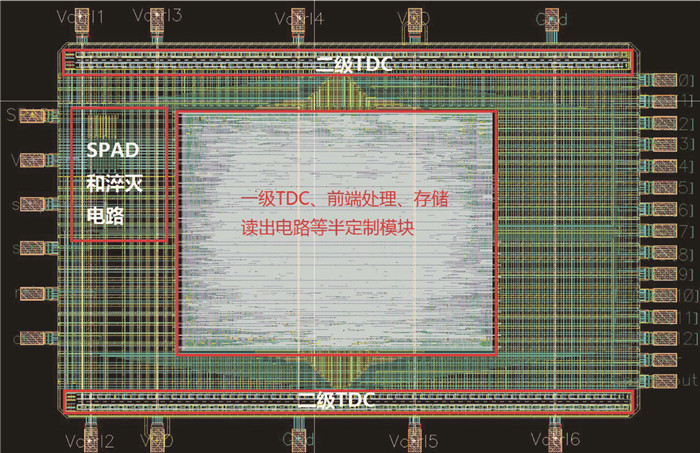

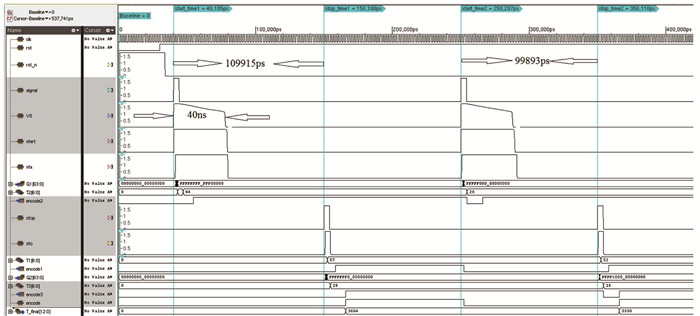

将完成的半定制模块版图和全定制模块版图进行拼接,得到单光子探测系统的完整版图,如图 10所示.版图面积为2 800 μm×1 900 μm.并在Cadence中搭建基于AMS的仿真环境对系统整体进行数模混合仿真,对两个荧光信号进行连续测量,仿真结果如图 11所示.

|

图 10 芯片版图 Fig. 10 Chip layout |

|

图 11 系统整体混合仿真结果 Fig. 11 System mixed simulation results |

由图 11可知,系统首先对复位信号进行处理,产生同步的全局复位信号rst_n,随后当激光信号signal到达,Vs电压迅速上升,完成SPAD的淬灭,同时产生TDC的开始信号start,随后Vs保持一段时间后迅速降到0 V,完成SPAD复位,淬灭电路的死时间大小约为40 ns.前端接口电路对CLK信号处理,输出为sta和sto,二级TDC测量start和sta、stop和sto两个时间间隔,分别输出温度码Q1[63: 0]和Q2[63: 0],编码电路将两个温度码转换为二进制码T2[6: 0]和T3[6: 0],并产生两个使能信号encode2和encode3.一级TDC计数start和stop之间的时钟周期个数输出为T1[6: 0],计数完成后产生使能信号encode1.当3个使能信号均有效时,即encode为高电平时,计算出最后结果T_final[12: 0].

第1次测量结果为

T测量1= (64×57+44-28) ×30 ps=3 664×30 ps= 109 920 ps≈T理论1=109 915 ps.

第2次测量结果为

T测量2= (64×52+20-18) ×30 ps= 3 330×30 ps= 99 900 ps≈T理论2=99 893 ps.

仿真结果表明,淬灭电路可以完成SPAD的淬灭和复位,测量死时间约为40 ns;TDC可以正确测量荧光信号的出现时间,两次测量误差均小于10 ps,可以保证30 ps的时间分辨率.

表 2列出了本文与部分文献中的基于TDC的单光子探测系统的性能对比.可以看到,本文设计的单光子探测系统工作频率较高,TDC的动态范围和测量精度明显提高,淬灭电路的死时间优化显著,整体综合性能提升明显.

| 表 2 基于TDC的单光子探测系统性能对比 Tab. 2 Comparison of performance of single photon detection system based on TDC |

1) TDC整体采用两级结构,实现了30 ps的时间分辨率和241 ns的动态范围.

2) 第2级TDC采用三通道游标型整体架构,结合差分结构的延时单元,将时间不确定度降低到传统结构的57%以下.

3) SPAD器件采用非接触保护环结构,击穿电压大约为11.3 V,雪崩击穿电流大于10-3A.

4) 淬灭电路结合主被动淬灭的优势,抑制后脉冲产生的同时使探测死时间小于40 ns.系统在526 MHz控制时钟下对两个荧光信号进行仿真测量,测量误差均小于10 ps.本文设计的单光子探测系统在工作频率、测量精度、测量范围和测量误差等方面具有一定的优势,能够应用于荧光寿命成像.

| [1] |

OKABE K, INADA N, GOTA C, et al. Intracellular temperature mapping with a fluorescent polymeric thermometer and fluorescence lifetime imaging microscopy[J]. Nature Communications, 2012, 3(5): 705. DOI:10.1038/ncomms1714 |

| [2] |

BEREZIN M Y, ACHILEFU S. Fluorescence lifetime measurements and biologicalimaging[J]. Chemical Reviews, 2010, 110(5): 2641. DOI:10.1021/cr900343z |

| [3] |

MARCU L. Fluorescence lifetime techniques in medicalapplications[J]. Annals of Biomedical Engineering, 2012, 40(2): 304. DOI:10.1007/s10439-011-0495-y |

| [4] |

WANG Xinlei, NIE Kaiming, QIAO Jun, et al. Modeling and simulation of time-gated FLIM SPAD image sensors[C]//Selected Papers from Conferences of the Photoelectronic Technology Committee of the Chinese Society of Astronautics 2014. Suzhou: SPIE, 2015: 990. DOI: 10.1117/12.2182158

|

| [5] |

JIN Xiangliang, TANG Lizhen, YANG Hongjiao, et al. Pixel design for time-of-flight range detector with time-to-digital converter[C]//Proceedings of the 12th IEEE International Conference on Solid-state and Integrated Circuit Technology. Guilin: IEEE, 2014: 876. DOI: 10.1109/ICSICT.2014.7021270

|

| [6] |

曹静, 张钊, 祁楠, 等. 用于LiDAR的16×1列阵CMOS单光子TOF图像传感器[J]. 光子学报, 2019, 48(7): 0704001. CAO Jing, ZHANG Zhao, QI Nan, et al. A 16×1 pixels 180 nm CMOS SPAD-based TOF image sensor for LiDAR applications[J]. Acta Photonica Sinica, 2019, 48(7): 0704001. |

| [7] |

NGUYEN V N, LEE J W. A low power two-step cyclic time-to-digital converter without startup time error in 180 nm CMOS[C]//Proceedings of the 2nd International Conference on Recent Advances in Signal Processing, Telecommunications and Computing. Ho Chi Minh: IEEE, 2018: 116. DOI: 10.1109/SIGTELCOM.2018.8325773

|

| [8] |

CHENG Zeng, DEEN M J, PENG Hao. A low-power gateable Vernier ring oscillator time-to-digital converter for biomedical imaging applications[J]. IEEE Transactions on Biomedical Circuits and Systems, 2016, 10(2): 445. DOI:10.1109/tbcas.2015.2434957 |

| [9] |

PANCHERI L, STOPPA D, DALLABETTA G F. Characterization and modeling of breakdown probability in sub-micrometer CMOS SPADs[J]. IEEE Journal of Selected Topics in Quantum Electronics, 2014, 20(6): 328. DOI:10.1109/jstqe.2014.2327791 |

| [10] |

LI D U, ARLT J, RICHARDSON J, et al. Real-time fluorescence lifetime imaging system with a 32×32 0.13 μm CMOS low dark-count single-photon avalanche diode array[J]. Optics Express, 2010, 18(10): 10257. DOI:10.1364/OE.18.010257 |

| [11] |

STOPPA D, MOSCONI D, PANCHERI L, et al. Single-photon avalanche diode CMOS sensor for time-resolved fluorescence measurements[J]. IEEE Sensors Journal, 2009, 9(9): 1084. DOI:10.1109/JSEN.2009.2025581 |

| [12] |

RICHARDSON J A, WEBSTER E A G, GRANT L A, et al. Scaleable single-photon avalanche diode structures in nanometer CMOS technology[J]. IEEE Transactions on Electron Devices, 2011, 58(7): 2028. DOI:10.1109/ted.2011.2141138 |

| [13] |

吴佳骏, 谢生, 毛陆虹, 等. 基于标准CMOS工艺的非接触式保护环单光子雪崩二极管[J]. 光子学报, 2018, 47(1): 0125001. WU Jiajun, XIE Sheng, MAO Luhong, et al. Single photon avalanche diode with non-contact guard ring based on CMOS technology[J]. Acta Photonica Sinica, 2018, 47(1): 0125001. DOI:10.3788/gzxb20184701.0125001 |

| [14] |

VILÀ A, VILELLA E, ALONSO O, et al. Crosstalk-free single photon avalanche photodiodes located in a shared well[J]. IEEE Electron Device Letters, 2014, 35(1): 99. DOI:10.1109/LED.2013.2288983 |

| [15] |

GIUSTOLISI G, GRASSO A D, PALUMBO G. Integrated quenching-and-reset circuit for single-photon avalanchediodes[J]. IEEE Transactions on Instrumentation and Measurement, 2015, 64(1): 271. DOI:10.1109/TIM.2014.2338652 |

| [16] |

侯强, 揭灿, 姚亚峰, 等. 一种结合高分辨率TDC的快速全数字锁相环设计[J]. 哈尔滨工业大学学报, 2018, 50(11): 83. HOU Qiang, JIE Can, YAO Yafeng, et al. A fast all digital phase-locked loop design with high resolution TDC[J]. Journal of Harbin Institute of Technology, 2018, 50(11): 83. DOI:10.11918/j.issn.0367-6234.201803148 |

2020, Vol. 52

2020, Vol. 52